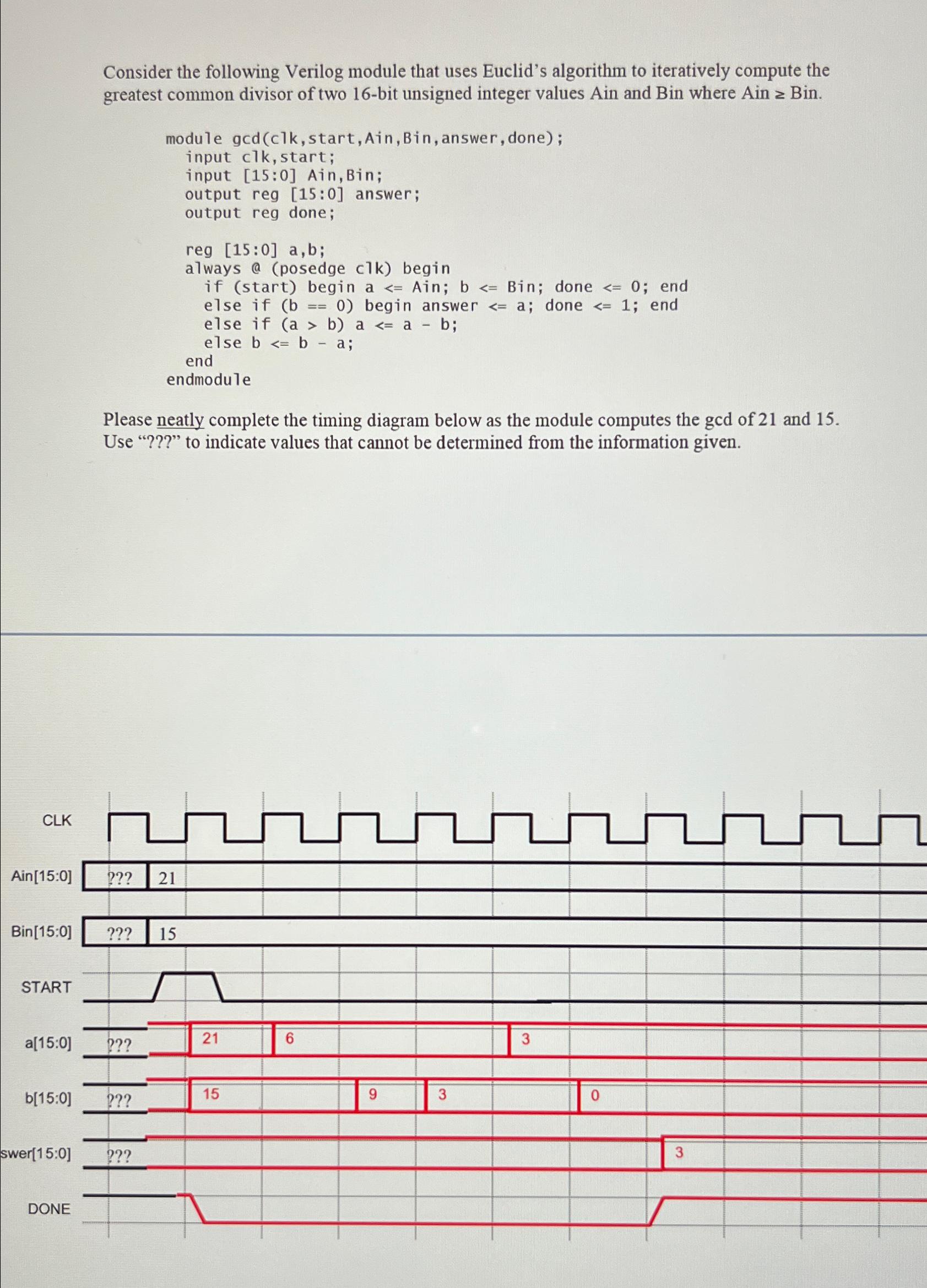

Question: Consider the following Verilog module that uses Euclid's algorithm to iteratively compute the greatest common divisor of two 1 6 - bit unsigned integer values

Step by Step Solution

There are 3 Steps involved in it

To complete the timing diagram using Euclids algorithm to find the GCD of 21 and 15 lets follow the ... View full answer

Get step-by-step solutions from verified subject matter experts