Question: 6 . Consider the following verilog modules. Module m 1 ( a , b , c , d ) ; Input a , b ,

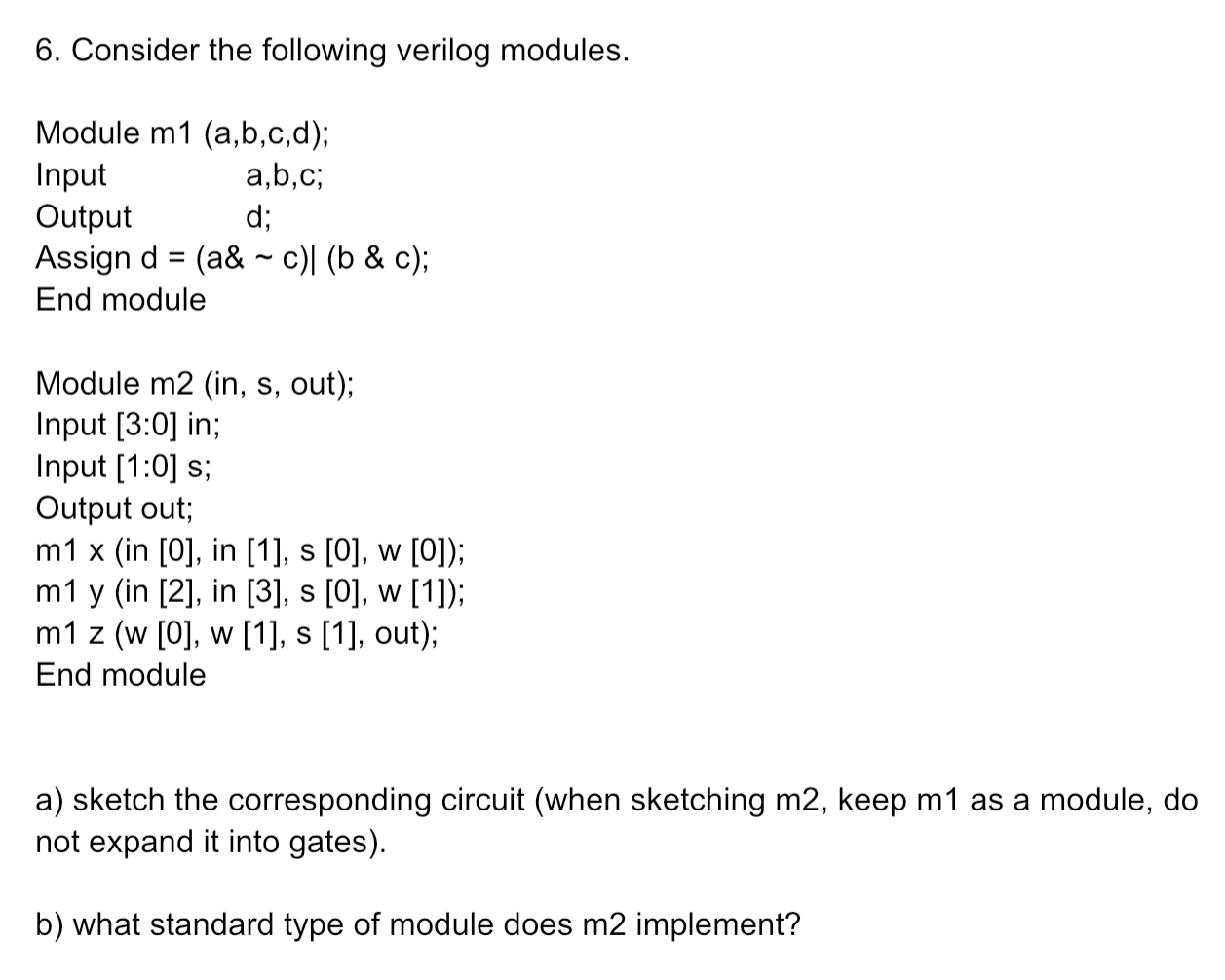

Consider the following verilog modules.

Module mabcd;

Input abc;

Output d;

Assign d a& ~ cb & c;

End module

Module min s out;

Input : in;

Input : s;

Output out;

m x in in s w ;

m y in in s w ;

m z w w s out;

End module

a sketch the corresponding circuit when sketching m keep m as a module, do not expand it into gates

b what standard type of module does m implement? Consider the following verilog modules.

Module mabcd;

Input abc;

Output d;

Assign da & sim cmidb & c;

End module

Module min s out;

Input : in;

Input : s;

Output out;

m x in in s w ;

m y in in s w ;

m z w w s out;

End module

a sketch the corresponding circuit when sketching m keep m as a module, do not expand it into gates

b what standard type of module does m implement?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock