Question: Consider the MIPS assembly language code segment given below. 11: add $s1, $s2, $s3 12: add $s2, $s1, $s4 13: add $s1, $s1, $s2

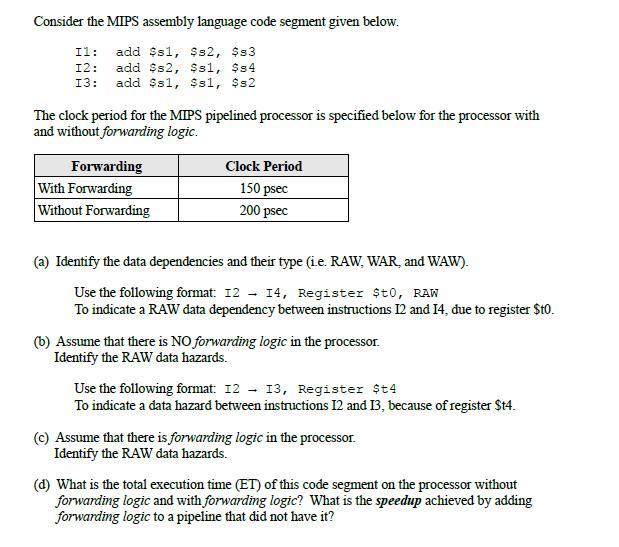

Consider the MIPS assembly language code segment given below. 11: add $s1, $s2, $s3 12: add $s2, $s1, $s4 13: add $s1, $s1, $s2 The clock period for the MIPS pipelined processor is specified below for the processor with and without forwarding logic. Forwarding With Forwarding Without Forwarding Clock Period 150 psec 200 psec (a) Identify the data dependencies and their type (ie. RAW, WAR, and WAW). Use the following format: 12 14, Register $t0, RAW To indicate a RAW data dependency between instructions 12 and 14, due to register $10. (b) Assume that there is NO forwarding logic in the processor. Identify the RAW data hazards. Use the following format: 12 - 13, Register $t4 To indicate a data hazard between instructions 12 and 13, because of register $t4. (c) Assume that there is forwarding logic in the processor. Identify the RAW data hazards. (d) What is the total execution time (ET) of this code segment on the processor without forwarding logic and with forwarding logic? What is the speedup achieved by adding forwarding logic to a pipeline that did not have it?

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts