Question: Consider the MIPS assembly language code segment given below. I1: lw $t0, 10($t1) 12: addi $t2, $t3, 2 13: sub $t4, $t5, $t6 14:

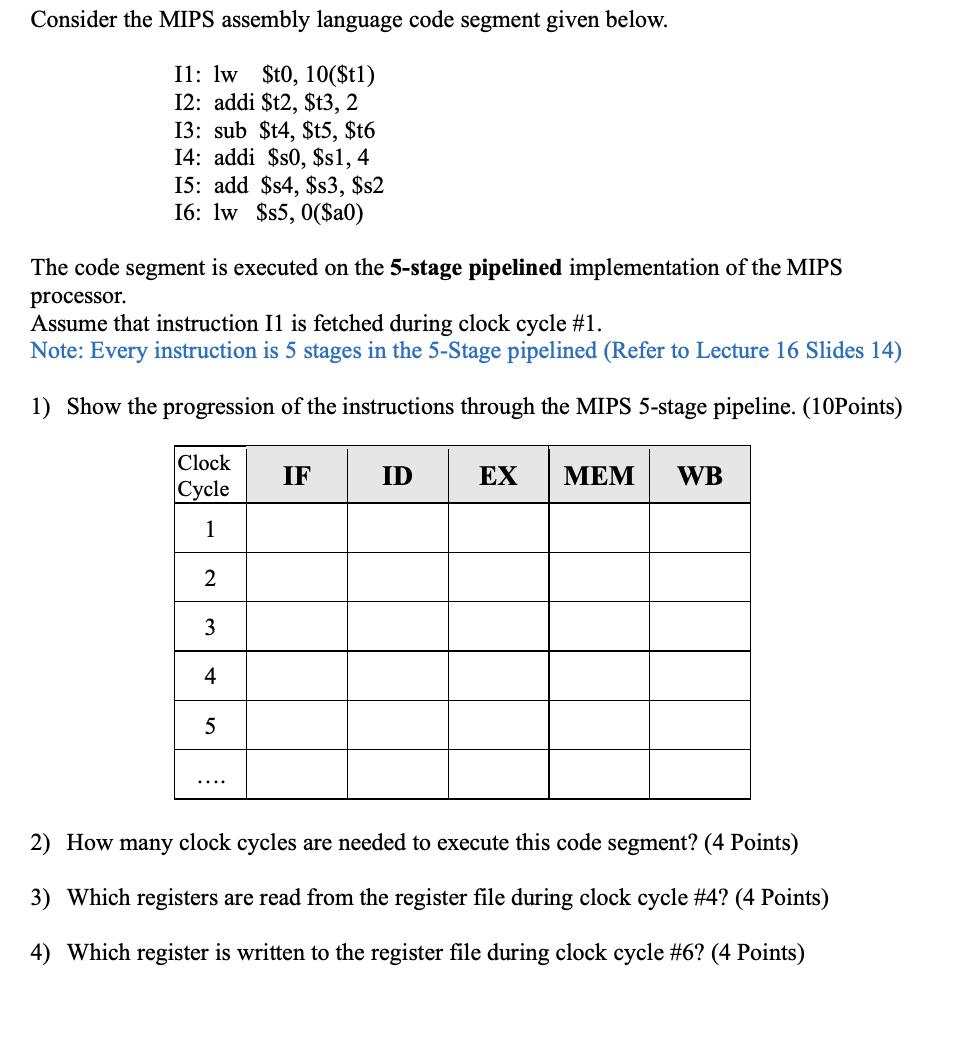

Consider the MIPS assembly language code segment given below. I1: lw $t0, 10($t1) 12: addi $t2, $t3, 2 13: sub $t4, $t5, $t6 14: addi $s0, $s1, 4 15: add $s4, $s3, $s2 16: lw $s5, 0($a0) The code segment is executed on the 5-stage pipelined implementation of the MIPS processor. Assume that instruction Il is fetched during clock cycle #1. Note: Every instruction is 5 stages in the 5-Stage pipelined (Refer to Lecture 16 Slides 14) 1) Show the progression of the instructions through the MIPS 5-stage pipeline. (10Points) Clock Cycle 1 2 3 4 5 IF ID EX MEM WB 2) How many clock cycles are needed to execute this code segment? (4 Points) 3) Which registers are read from the register file during clock cycle #4? (4 Points) 4) Which register is written to the register file during clock cycle #6? (4 Points)

Step by Step Solution

3.54 Rating (157 Votes )

There are 3 Steps involved in it

Ans 1 Clock Cycles 3556 7 8 10 if I 12 13 ID EX 12 TL Ty 13 12 15 T... View full answer

Get step-by-step solutions from verified subject matter experts