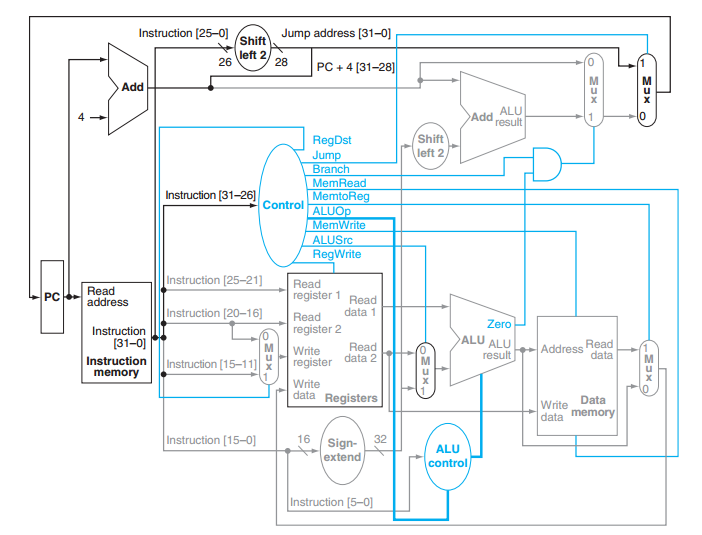

Question: Consider the single-cycle MIPS, where sequential elements are initialized as follows: $t1=12, $t5=13, and DataRAM[i]=2i . Suppose you are executing the instruction lw $t1,0x1234($t5). Label

Consider the single-cycle MIPS, where sequential elements are initialized as follows: $t1=12, $t5=13, and DataRAM[i]=2i . Suppose you are executing the instruction lw $t1,0x1234($t5). Label each wire/bus in the architecture with the value being transmitted on the line (do this for both data and control signals).

Shift Jump address (31-o] left 2 Instruction [25-0] 26 28 PC+4131-28) UI ALU Add RegDst Shift left 2 ra MemRead nstructionl312control|ALU0 MemWrite ALUSrc RegWrite Instruction [25-21]Read register 1 Read Readdata 1 PCaddress Instruction [20-16] Zero register 2 ALU ALUn_ Address dai 31-0] Instruction Instruction [15-11register Read Write Read -| M result data 2 UI Write data Registers Write Data data memory nstruction [15-0] 16 Sign- 32 ALU control Instruction [5-0] Shift Jump address (31-o] left 2 Instruction [25-0] 26 28 PC+4131-28) UI ALU Add RegDst Shift left 2 ra MemRead nstructionl312control|ALU0 MemWrite ALUSrc RegWrite Instruction [25-21]Read register 1 Read Readdata 1 PCaddress Instruction [20-16] Zero register 2 ALU ALUn_ Address dai 31-0] Instruction Instruction [15-11register Read Write Read -| M result data 2 UI Write data Registers Write Data data memory nstruction [15-0] 16 Sign- 32 ALU control Instruction [5-0]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts