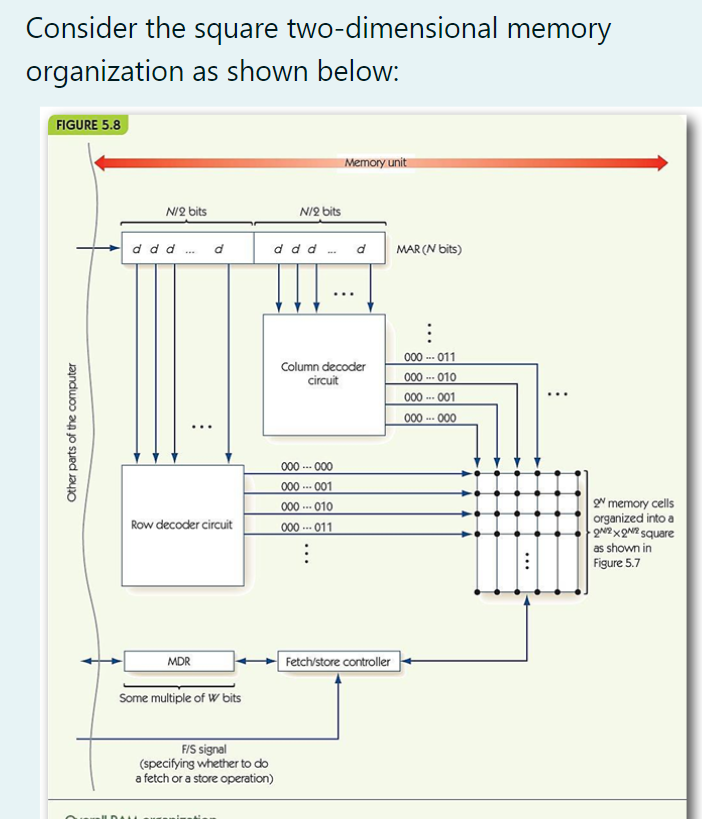

Question: Consider the square two-dimensional memory organization as shown below: FIGURE 5.8 Memory unit N/2 bits N/2 bits ddd d ddd d MAR (N bits) Column

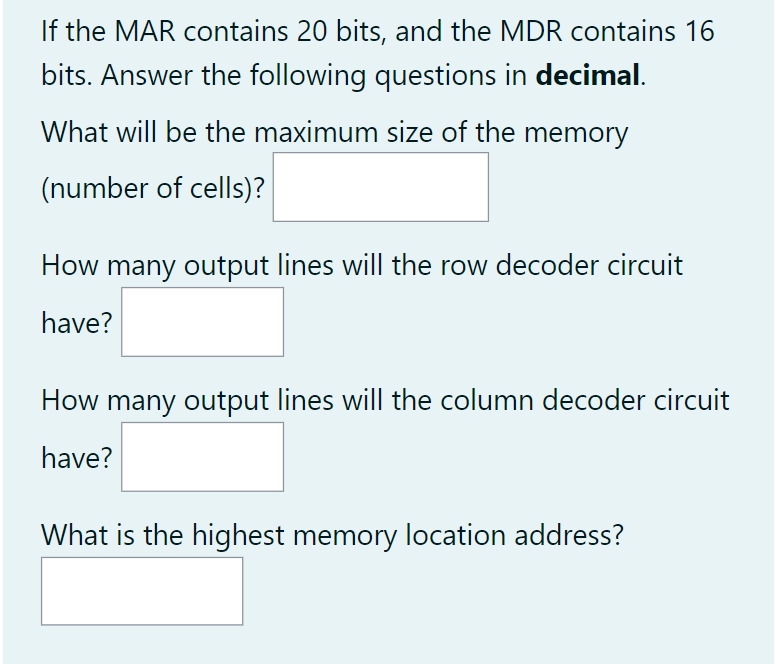

Consider the square two-dimensional memory organization as shown below: FIGURE 5.8 Memory unit N/2 bits N/2 bits ddd d ddd d MAR (N bits) Column decoder circuit : 000 -- 011 000 -- 010 000 --- 001 000 ... 000 Other parts of the computer 000 ... 000 000...001 000 ... 010 000 ... 011 Row decoder circuit 2 memory cells organized into a 2N2X2N2 square as shown in Figure 5.7 ... MDR Fetchystore controller Some multiple of W bits F/S signal (specifying whether to do a fetch or a store operation) If the MAR contains 20 bits, and the MDR contains 16 bits. Answer the following questions in decimal. What will be the maximum size of the memory (number of cells)? How many output lines will the row decoder circuit have? How many output lines will the column decoder circuit have? What is the highest memory location address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts