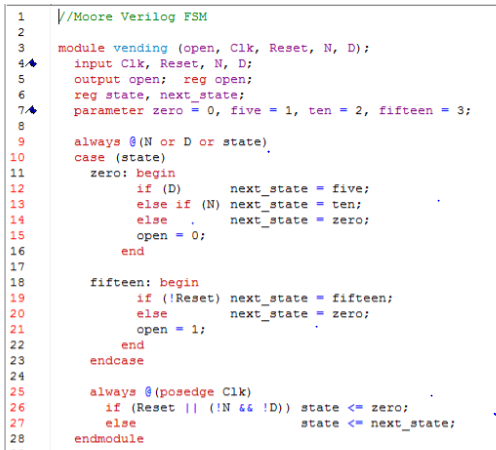

Question: Could someone help me create a test bench for my assembly code /Moore Verilog FSM 2 3 module vending (open, Cik, Reset, N, D) input

Could someone help me create a test bench for my assembly code

/Moore Verilog FSM 2 3 module vending (open, Cik, Reset, N, D) input Clk, Reset, N, D; output open: reg open: reg state, next state: parameter zero-o, five-1, ten= 2, fifteen = 3; 4A 6 74 always (N or D or state) case (state) 9 10 zero: begin 12 13 14 15 16 17 18 19 20 21 if (D) e13e if (N) next 3tate ten ; else open = 0; next_state-five: next state-zero end fifteen: begin f (Reset) next state-fifteen; else open = 1; nextstate = zero; - end endcase 23 24 25 26 27 28 always (posedge Cik) if (Reset 11 (IN &&D) state

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts