Question: Create a code in VHDL For this project you will design a First In First Out (FIFO) Register storage queue with a total of 16

Create a code in VHDL

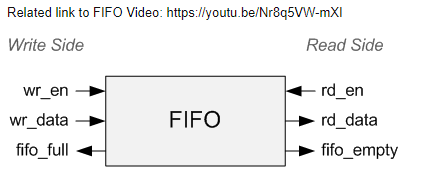

For this project you will design a First In First Out (FIFO) Register storage queue with a total of 16 FIFO-ordered Four-Bit Registers and accessible through two independent interfaces or ports.

The Model should be able to accept Write_H Commands for data presented at it's Data_In_H (3:0) port until the FIFO is Full which should be indicated by asserting a Full_H out status signal.

The model should be able to accept Read_H Commands with data showing at the Data_Out_H (3:0) port until the FIFO is Empty which should be indicated by asserting an Empty_H out signal.

Considering that this FIFO might be accessed by separate entities on it's independent Read and Write ports, it should provide a Write_Done_H and a Read_Done_H signals on its ports.

The model should Arbitrate between possibly simultaneous Read_H commands and Write_H commands such that:

1.If the FIFO is Full a Read_H command request should receive priority over a Write_H request which should not be replied-to

2- If the FIFO is Empty a Write_H command request should receive priority over a Read_H request which should not be replied-to

3-If the FIFO is not Empty nor Full, and there are concurrent Read_H and Write_H command requests, these should receive ALTERNATE priorities (round- robin).

4- If the FIFO is not Empty nor Full, and there is only one command request, it should be served immediately

5- If there are no Read_H, nor Write_H requests the FIFO should stay iddle waiting for a command.

FIFO readers and writers should not initiate a new Read_H or Write_H command until the previous command is acknowledged on the respective input(write) or output(read) port.

You will obviously need to use the Register model already developed as part of this digital system Data Path, also the Counter model might be useful to keep track of how many FIFO registers are filled with valid data, and/or which is the register at the Head or which at the Tail of the FIFO. You might also need to use tri-state buffers(TSBs) to selectively enable each register to the output bus, and to use the FF model for the Full and Empty flags. Note that these flags will be set and readback by your own FSM on various states. You might also want to use decoders that decode the outputs of the counters that identify which register should be loaded with the input write data or which register output should be enabled into the output read data. As a hint you can adopt one of two architectural strategies to assure that data inside the FIFO is packed in consecutive locations either at the entrance (in which case you shift into the first FIFO registers every Data_in item and use a counter to keep track which is the FIFO register at the Head), or packed in consecutive locations at the exit (in which case you always shift out-of the last register in the FIFO in a Read

Related link to FIFO Video: https:/lyoutu.be/Nr8q5VW-mXI Write Side Read Side rd en wr en wr data- fifo full FIFO rd_data fifo_empty

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts