Question: Data path and latency The table below shows a list of MIPS instructions and the resources in the data path. Assume the latency for Instruction

Data path and latency

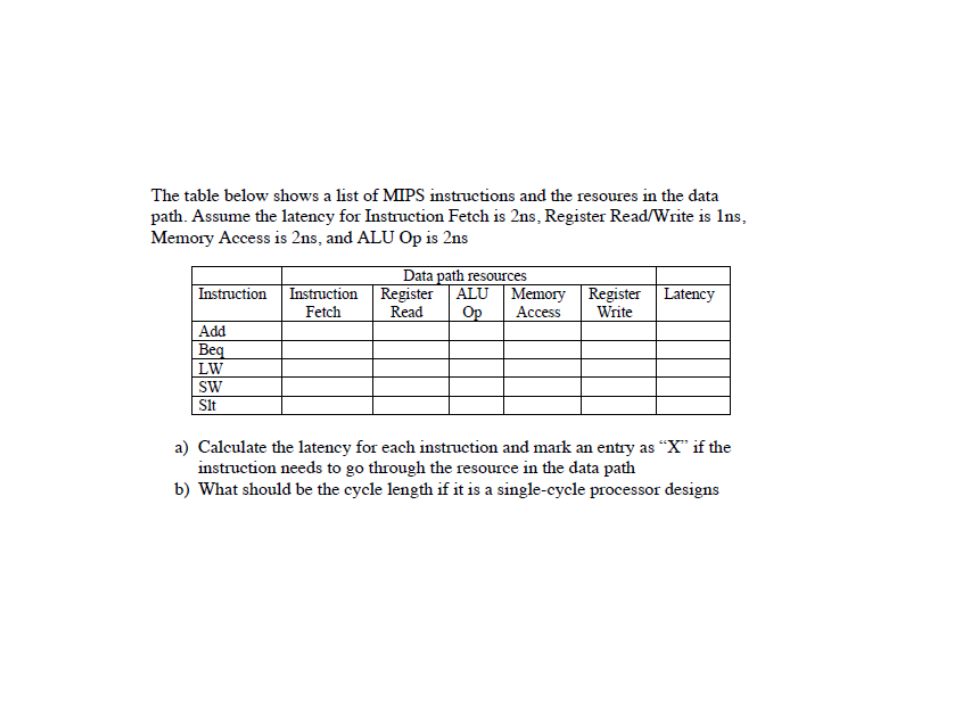

The table below shows a list of MIPS instructions and the resources in the data path. Assume the latency for Instruction Fetch is 2ns, Register Read/Write is 1ns, Memory Access is 2ns, and ALU Op is 2ns.

a) Calculate the latency for each instruction and mark an entry as X if the instruction needs to go through the resource in the data path b) What should be the cycle length if it is a single-cycle processor designs

The table below shows a list of MIPS instructions and the resources in the data path. Assume the latency for Instruction Fetch is 2ns, Register Read/Write is Ins, Memory Access is 2ns, and ALU Op is 2ns a) Calculate the latency for each instruction and mark an entry as "X" if the instruction needs to go through the resource in the data path b) What should be the cycle length if it is a single-cycle processor designs

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts