Question: Computer Organization Q3. 4.4 Problems in this exercise assume that logic blocks needed to implement a processor's data path have the following latencies: I-Mem Add

Computer Organization

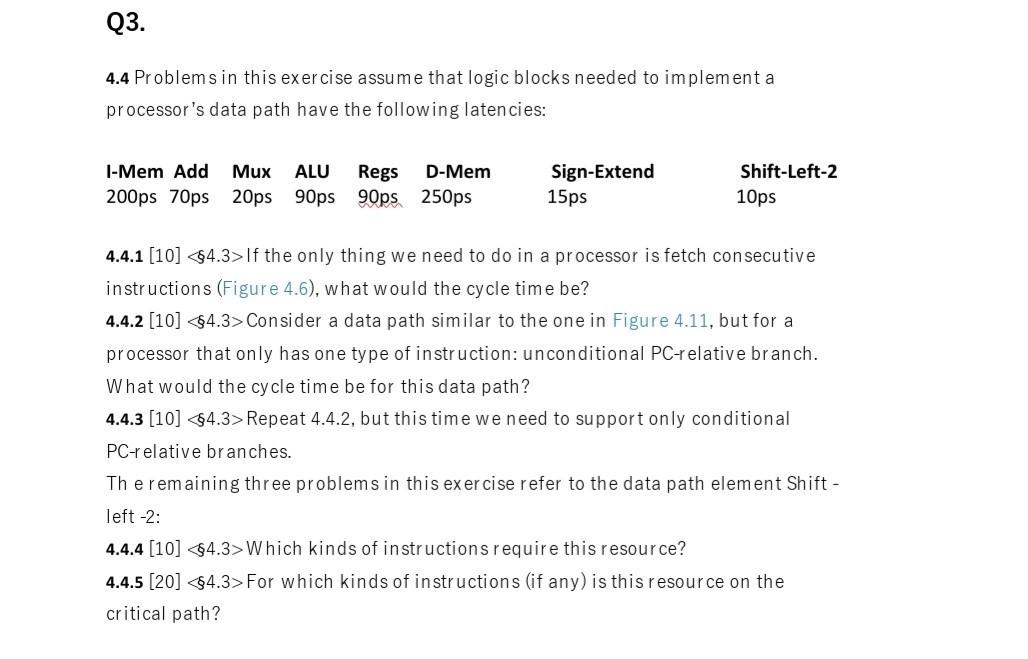

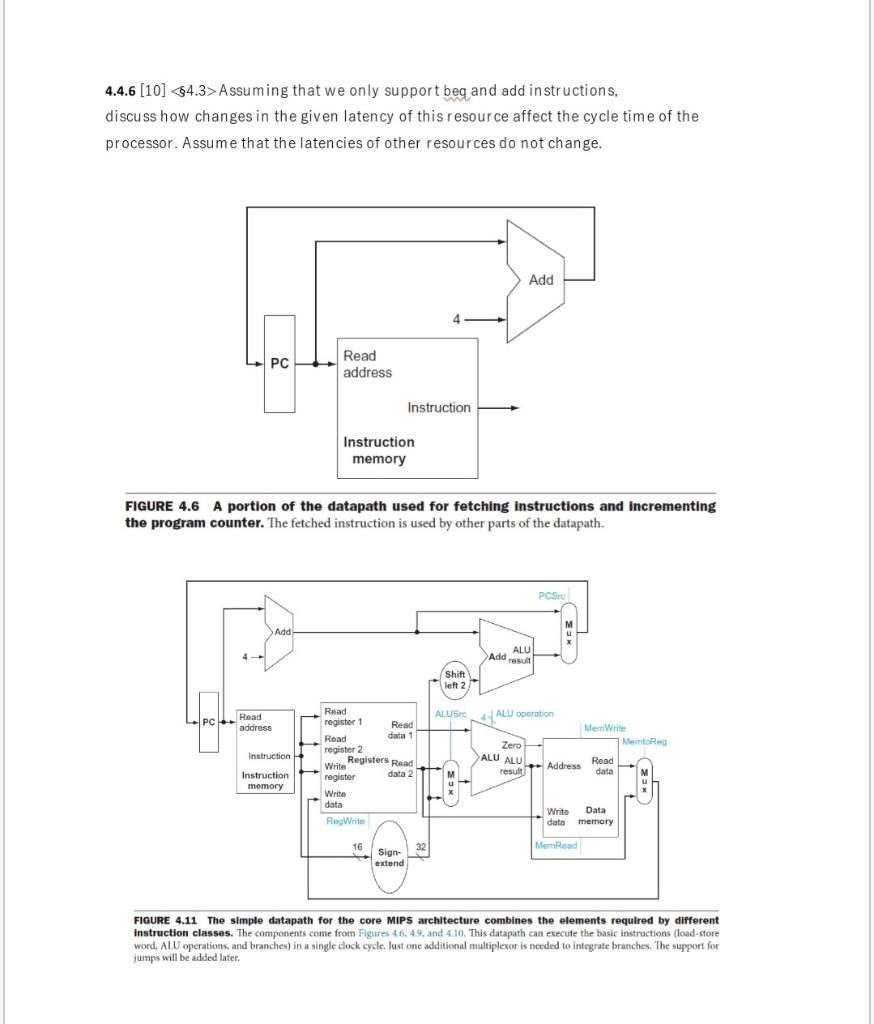

Q3. 4.4 Problems in this exercise assume that logic blocks needed to implement a processor's data path have the following latencies: I-Mem Add Mux ALU 200ps 70ps 20ps 90ps Regs D-Mem 90ps 250ps Sign-Extend 15ps Shift-Left-2 10ps 4.4.1 [10] $4.3>If the only thing we need to do in a processor is fetch consecutive instructions (Figure 4.6), what would the cycle time be? 4.4.2 [10] $4.3> Consider a data path similar to the one in Figure 4.11, but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this data path? 4.4.3 (10) $4.3>Repeat 4.4.2, but this time we need to support only conditional PC-relative branches. The remaining three problems in this exercise refer to the data path element Shift - left-2: 4.4.4 (10) $4.3> Which kinds of instructions require this resource? 4.4.5 [20] For which kinds of instructions (if any) is this resource on the critical path? 4.4.6 [10] $4.3> Assuming that we only support beg and add instructions, discuss how changes in the given latency of this resource affect the cycle time of the processor. Assume that the latencies of other resources do not change. Add PC Read address Instruction Instruction memory FIGURE 4.6 A portion of the datapath used for fetching Instructions and incrementing the program counter. The fetched instruction is used by other parts of the datapath. PCS > Add ALU 4 - Add result Shift left 2 PC. Read ALUSTALU operation address Read data 1 Mem Write MamtoRed Zero Instruction Registers Read ALU ALU Read register 1 Road register 2 Write register Write data RegWrite Read data data 2 result Address M Instruction memory Write Data data memory 16 32 MemRead Sign- extend FIGURE 4.11 The simple datapath for the core MIPS architecture combines the elements required by different Instruction classes. The components come from Figures 46. 49, and 4.10. This datapath can execute the basic instructions (load-store word, ALU operations and branches) in a single cock cycle. Just one additional multiplecor is needed to integrate branches. The support for jumps will be added later

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts