Question: Design a clocked synchronous finite state machine with one input A , and one output X . The output is asserted ( for one clock

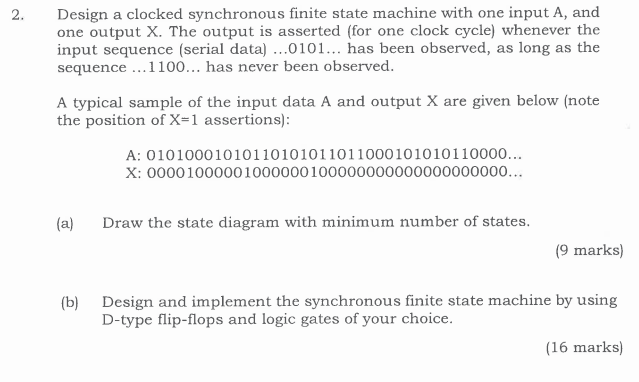

Design a clocked synchronous finite state machine with one input A and

one output X The output is asserted for one clock cycle whenever the

input sequence serial data has been observed, as long as the

sequence has never been observed.

A typical sample of the input data A and output are given below note

the position of assertions:

A: dots

X: dots

a Draw the state diagram with minimum number of states.

marks

b Design and implement the synchronous finite state machine by using

Dtype flipflops and logic gates of your choice.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock