Question: Design a clocked synchronous state machine for a combinational lock with two inputs (X and Y) and one output (Z). Input X is used to

Design a clocked synchronous state machine for a combinational lock with two inputs (X and Y) and one output (Z). Input X is used to initialise the sequence entry. Input Y is used to enter the binary sequence to unlock. Output Z will be turned on if and only if the binary sequence is entered in proper order after the initialisation and must remain on as long as X input remains high. This combinational lock operates as follows. Input X must have changed from low to high in the previous clock period and should remain high afterwards (Initialisation). Entry of first binary digit must be done before the next clock cycle starts and entry of the remaining digits is done on the subsequent clocks. If a wrong sequence is entered, it will require re-initialising to start entering the correct sequence. Use the BCD code of last two digits of your student number (which is 64) as the binary sequence to open the lock with the least significant bit as the first entry of the sequence. You must implement your design in a PLD and demonstrate the operation to your instructor to pass this task.

The following is required:

Correct State Diagram Correct design steps, K-maps and minimised Boolean Expressions Correct PLD and simulation files

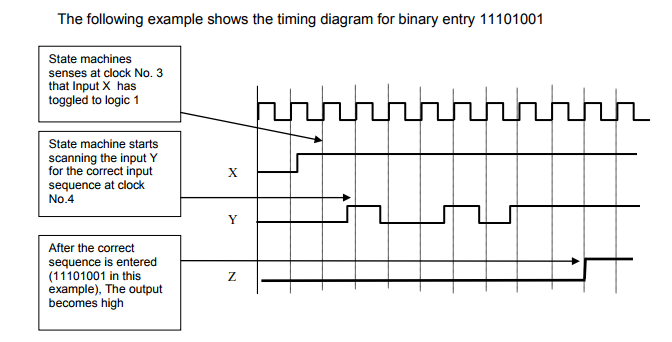

The following example shows the timing diagram for binary entry 11101001 State machines senses at clock No. 3 that Input X has toggled to logic 1 State machine starts scanning the input Y for the correct input sequence at clock No.4 After the correct sequence is entered (11101001 in this example), The output becomes high

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts