Question: Design a digital system that multiplies two unsigned binary numbers by the repeated addition method. For example, to multiply 5 by 4, it adds the

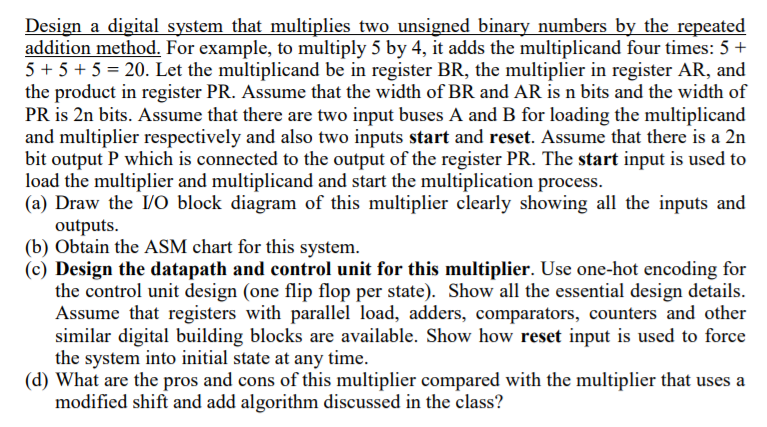

Design a digital system that multiplies two unsigned binary numbers by the repeated addition method. For example, to multiply 5 by 4, it adds the multiplicand four times: 5 + 5 +5 +5-20. Let the multiplicand be in register BR, the multiplier in register AR, and the product in register PR. Assume that the width of BR and AR is n bits and the width of PR is 2n bits. Assume that there are two input buses A and B for loading the multiplicand and multiplier respectively and also two inputs start and reset. Assume that there is a 2n bit output P which is connected to the output of the register PR. The start input is used to load the multiplier and multiplicand and start the multiplication process. (a) Draw the I/O block diagram of this multiplier clearly showing all the inputs and outputs (b) Obtain the ASM chart for this systemm (c) Design the datapath and control unit for this multiplier. Use one-hot encoding for the control unit design (one flip flop per state). Show all the essential design details Assume that registers with parallel load, adders, comparators, counters and other similar digital building blocks are available. Show how reset input is used to force the system into initial state at any time. (d) What are the pros and cons of this multiplier compared with the multiplier that uses a modified shift and add algorithm discussed in the class? Design a digital system that multiplies two unsigned binary numbers by the repeated addition method. For example, to multiply 5 by 4, it adds the multiplicand four times: 5 + 5 +5 +5-20. Let the multiplicand be in register BR, the multiplier in register AR, and the product in register PR. Assume that the width of BR and AR is n bits and the width of PR is 2n bits. Assume that there are two input buses A and B for loading the multiplicand and multiplier respectively and also two inputs start and reset. Assume that there is a 2n bit output P which is connected to the output of the register PR. The start input is used to load the multiplier and multiplicand and start the multiplication process. (a) Draw the I/O block diagram of this multiplier clearly showing all the inputs and outputs (b) Obtain the ASM chart for this systemm (c) Design the datapath and control unit for this multiplier. Use one-hot encoding for the control unit design (one flip flop per state). Show all the essential design details Assume that registers with parallel load, adders, comparators, counters and other similar digital building blocks are available. Show how reset input is used to force the system into initial state at any time. (d) What are the pros and cons of this multiplier compared with the multiplier that uses a modified shift and add algorithm discussed in the class

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts