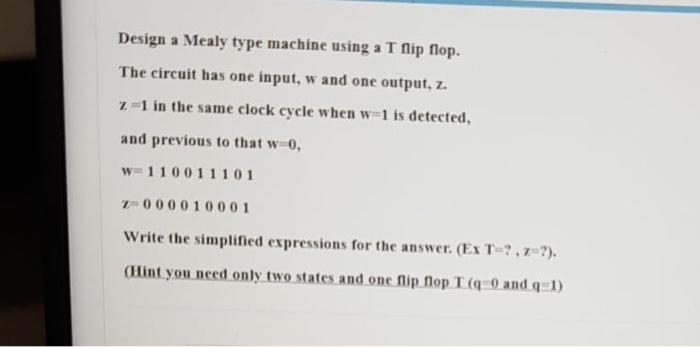

Question: Design a Mealy type machine using a T hip flop. The circuit has one input, w and one output, z. z=1 in the same clock

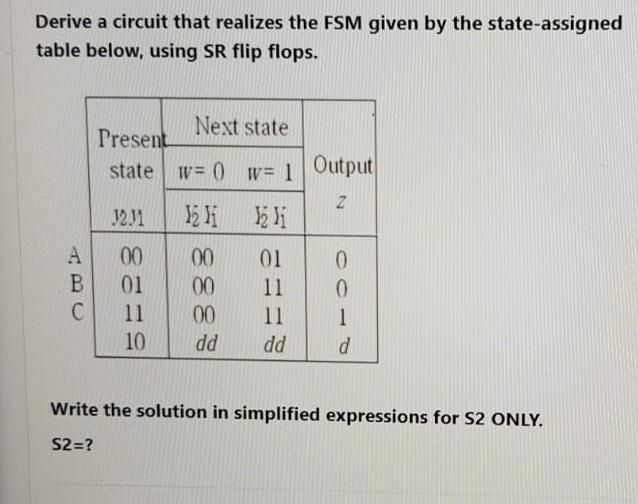

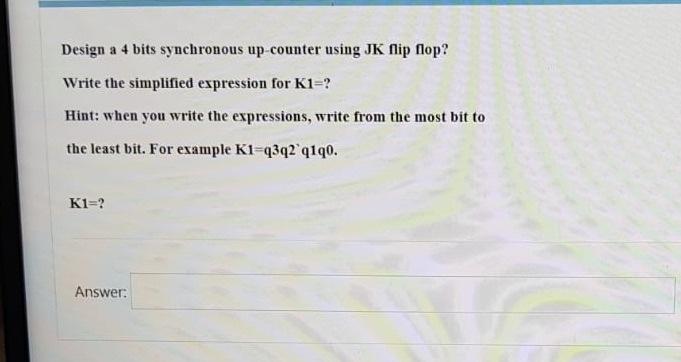

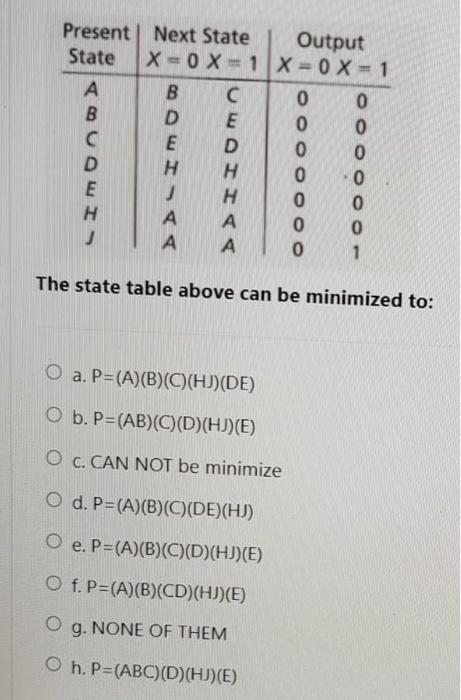

Design a Mealy type machine using a T hip flop. The circuit has one input, w and one output, z. z=1 in the same clock cycle when w 1 is detected, and previous to that w0, W-110011101 2000010001 Write the simplified expressions for the answer. (ExT-?, 7-?). (Hint you need only two states and one Nip flop Tq0 and q 1) Derive a circuit that realizes the FSM given by the state-assigned table below, using SR flip flops. Next state Present state w= 0) i= 1 Output Z J2J1 00 00 01 0 01 00 11 0 11 00 11 1 10 dd dd d A B C Write the solution in simplified expressions for S2 ONLY. S2=? Design a 4 bits synchronous up-counter using JK flip flop? Write the simplified expression for K1=? Hint: when you write the expressions, write from the most bit to the least bit. For example K1=q3q2'q1q0. K1=? Answer: Present Next State Output State X-OX=1 X=0X-1 B C 0 B D E 0 E D 0 D H H 0 E H 0 H A 0 A A 1 The state table above can be minimized to: O a. P=(A)(B)(C)(HJ)(DE) O b. P=(AB)(C)(D(HJ)(E) O C. CAN NOT be minimize O d. P=(A)(B)(C)(DE)(HJ) O e. P=(A)(B)(C)(D(H)(E) O f.P=(A)(B)(CD)(HJ)(E) O g. NONE OF THEM O h. P=(ABC)(D) (HJ)(E)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts