Question: DRAM ( Dynamic Random-Access Memory ): VHDL : 1. Create a vhdl file, based on the infromation given above for the DRAM: DRAM.vhd file which

DRAM (Dynamic Random-Access Memory):

VHDL :

1. Create a vhdl file, based on the infromation given above for the "DRAM":

DRAM.vhd file which contains a VHDL description of the RAM memory.

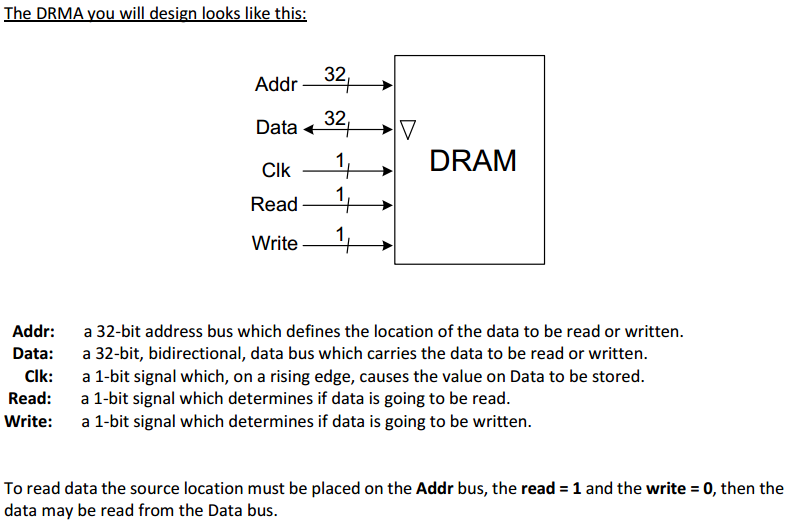

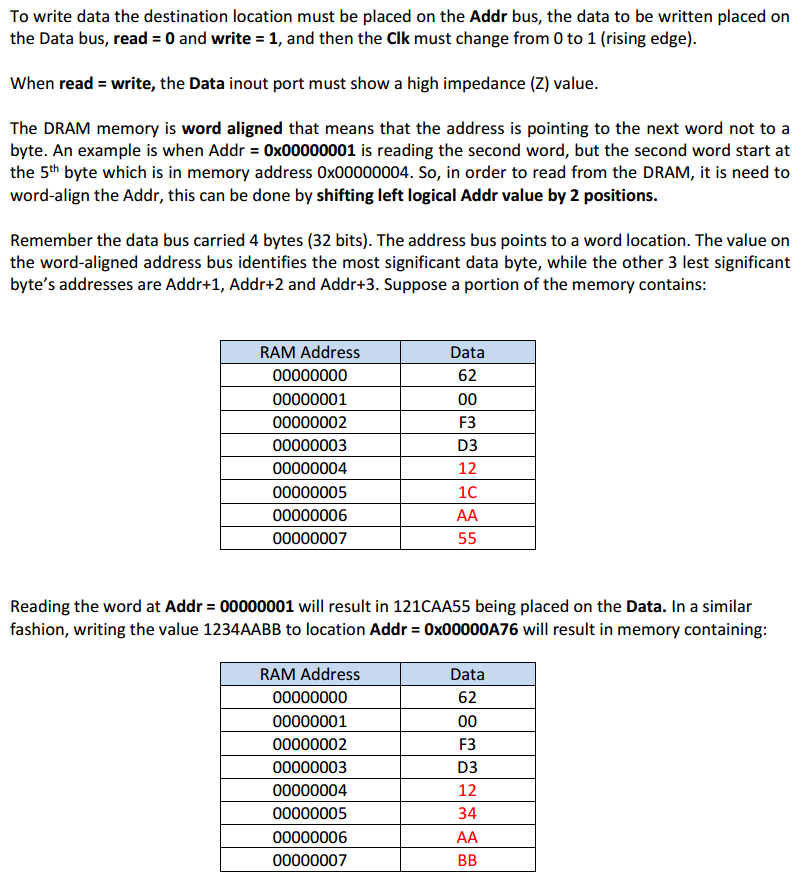

Addr 32 32 Clk1 Read-It- Write- 1 Addr: a 32-bit address bus which defines the location of the data to be read or writter Data: a 32-bit, bidirectional, data bus which carries the data to be read or written Clk a 1-bit signal which, on a rising edge, causes the value on Data to be stored. Read: a 1-bit signal which determines if data is going to be read Write: a 1-bit signal which determines if data is going to be written. To read data the source location must be placed on the Addr bus, the read 1 and the write 0, then the data may be read from the Data bus Addr 32 32 Clk1 Read-It- Write- 1 Addr: a 32-bit address bus which defines the location of the data to be read or writter Data: a 32-bit, bidirectional, data bus which carries the data to be read or written Clk a 1-bit signal which, on a rising edge, causes the value on Data to be stored. Read: a 1-bit signal which determines if data is going to be read Write: a 1-bit signal which determines if data is going to be written. To read data the source location must be placed on the Addr bus, the read 1 and the write 0, then the data may be read from the Data bus

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts