Question: Exercise 4: The multi-cycle and pipelined datapaths have generally been broken down into 5 steps: 1. Hardware to support an instruction fetch 2. Hardware to

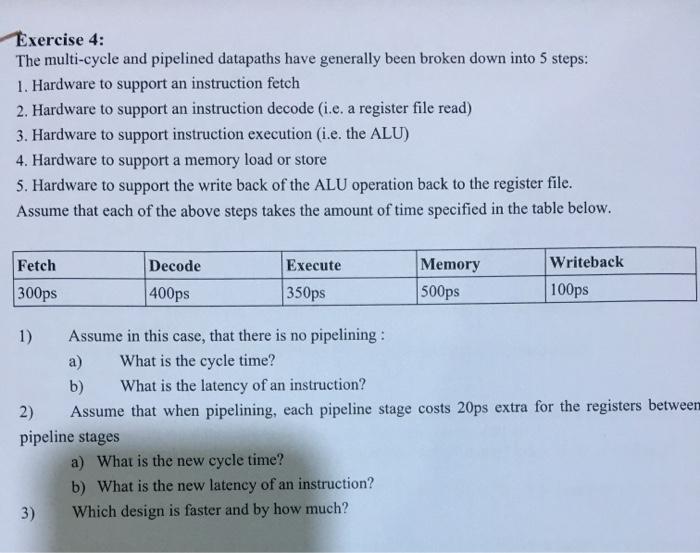

Exercise 4: The multi-cycle and pipelined datapaths have generally been broken down into 5 steps: 1. Hardware to support an instruction fetch 2. Hardware to support an instruction decode (i.e. a register file read) 3. Hardware to support instruction execution (i.e. the ALU) 4. Hardware to support a memory load or store 5. Hardware to support the write back of the ALU operation back to the register file. Assume that each of the above steps takes the amount of time specified in the table below. Fetch Decode 400ps Execute 350ps Memory 500ps Writeback 100ps 300ps 1) Assume in this case, that there is no pipelining: a) What is the cycle time? b) What is the latency of an instruction? 2) Assume that when pipelining, each pipeline stage costs 20ps extra for the registers between pipeline stages a) What is the new cycle time? b) What is the new latency of an instruction? 3) Which design is faster and by how much

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts