Question: EXERCISES Which modules generate the IRQ 0 , IRQ 1 0 and IRQ 3 1 interrupt requests, and what are their CMSIS typedef enumeration labels?

EXERCISES

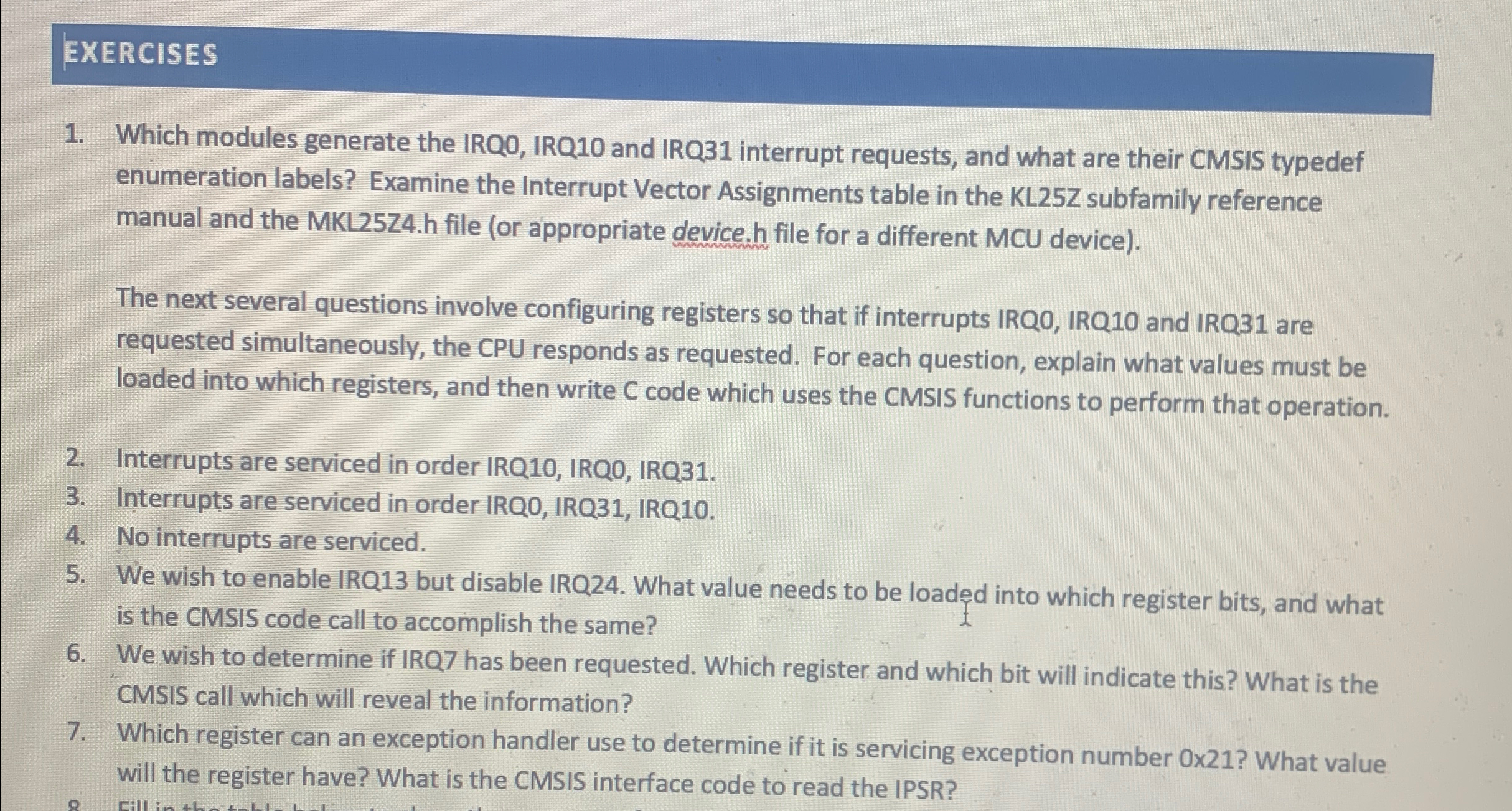

Which modules generate the IRQ IRQ and IRQ interrupt requests, and what are their CMSIS typedef enumeration labels? Examine the Interrupt Vector Assignments table in the KLZ subfamily reference manual and the MKLZh file or appropriate device.h file for a different MCU device

The next several questions involve configuring registers so that if interrupts IRQ IRQ and IRQ are requested simultaneously, the CPU responds as requested. For each question, explain what values must be loaded into which registers, and then write C code which uses the CMSIS functions to perform that operation.

Interrupts are serviced in order IRQ IRQ IRQ

Interrupts are serviced in order IRQ IRQ IRQ

No interrupts are serviced.

We wish to enable IRQ but disable IRQ What value needs to be loaded into which register bits, and what is the CMSIS code call to accomplish the same?

We wish to determine if IRQ has been requested. Which register and which bit will indicate this? What is the CMSIS call which will reveal the information?

Which register can an exception handler use to determine if it is servicing exception number What value will the register have? What is the CMSIS interface code to read the IPSR?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock