Question: fast please Consider scalar (non-pipeline) processor with same stages discussed in lecture: 1F, ID, EX, MEM and WB. Assume time for all stages is 100ps,

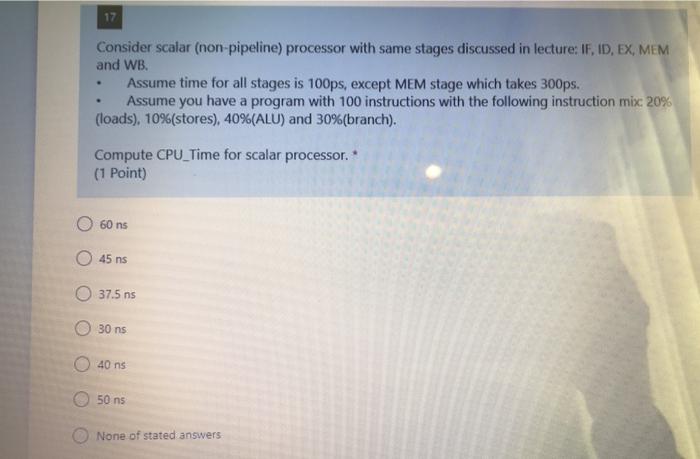

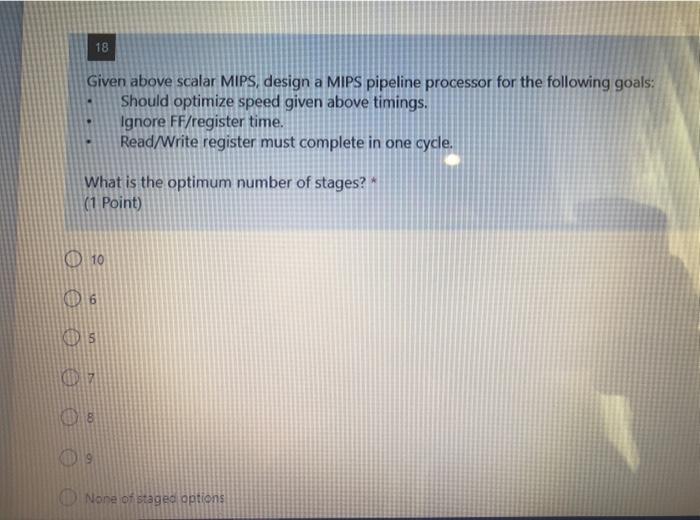

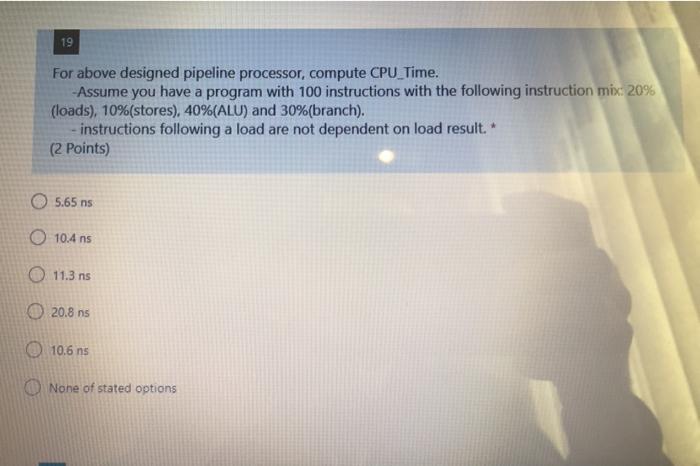

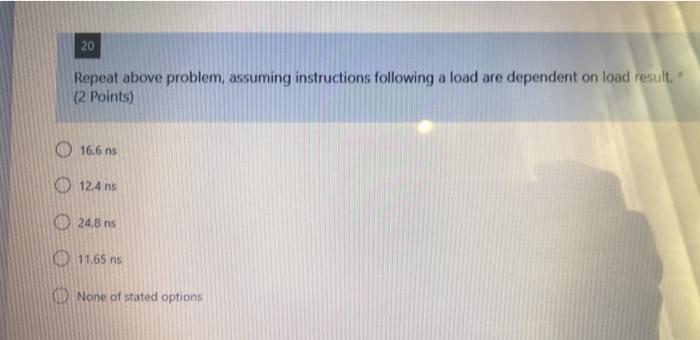

Consider scalar (non-pipeline) processor with same stages discussed in lecture: 1F, ID, EX, MEM and WB. Assume time for all stages is 100ps, except MEM stage which takes 300ps. Assume you have a program with 100 instructions with the following instruction mix 20% (loads), 10%(stores), 40%(ALU) and 30%(branch). Compute CPU_Time for scalar processor. (1 Point) 60 ns 45 ns 0 37.5 ns O 30 ns 40 ns 50 ns None of stated answers 18 Given above scalar MIPS, design a MIPS pipeline processor for the following goals: Should optimize speed given above timings. Ignore FF/register time. Read/Write register must complete in one cycle. What is the optimum number of stages? (1 Point) 10 06 05 08 None of stage options 19 For above designed pipeline processor, compute CPU_Time. Assume you have a program with 100 instructions with the following instruction mix: 20% (loads), 10%(stores), 40%(ALU) and 30%(branch). instructions following a load are not dependent on load result. (2 points) 5.65 ns 10.4 ns 11.3 ns 20.8 ns O 10.6 ns None of stated options 20 Repeat above problem, assuming instructions following a load are dependent on load result. (2 points) 16.6 ns 12.4 ns 24.8 ns 11.65 ns None of stated options

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts