Question: Given the following instruction sequence for the MIPS processor with the standard 5 stage pipeline, addi $ 1 0 , $ 0 , 4 lw

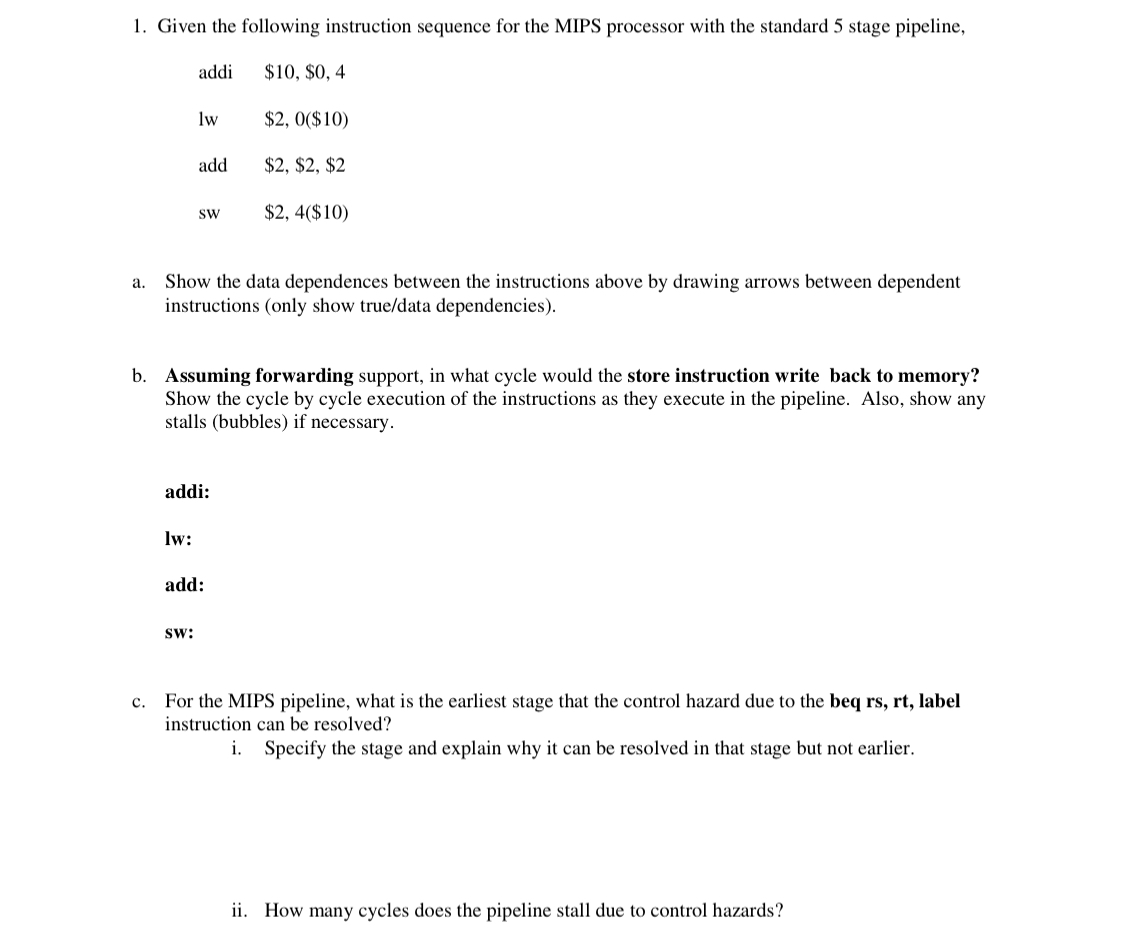

Given the following instruction sequence for the MIPS processor with the standard stage pipeline,

addi $$

lw $$

add $$$

sw $$

a Show the data dependences between the instructions above by drawing arrows between dependent

instructions only show truedata dependencies

b Assuming forwarding support, in what cycle would the store instruction write back to memory?

Show the cycle by cycle execution of the instructions as they execute in the pipeline. Also, show any

stalls bubbles if necessary.

addi:

lw:

add:

sw:

c For the MIPS pipeline, what is the earliest stage that the control hazard due to the beq rs rt label

instruction can be resolved?

i Specify the stage and explain why it can be resolved in that stage but not earlier.

ii How many cycles does the pipeline stall due to control hazards?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock