Question: Hand Written Solution Please Write the simulation results for the following VHDL code (fill in the table with 1 or 0). The propagation delay of

Hand Written Solution Please

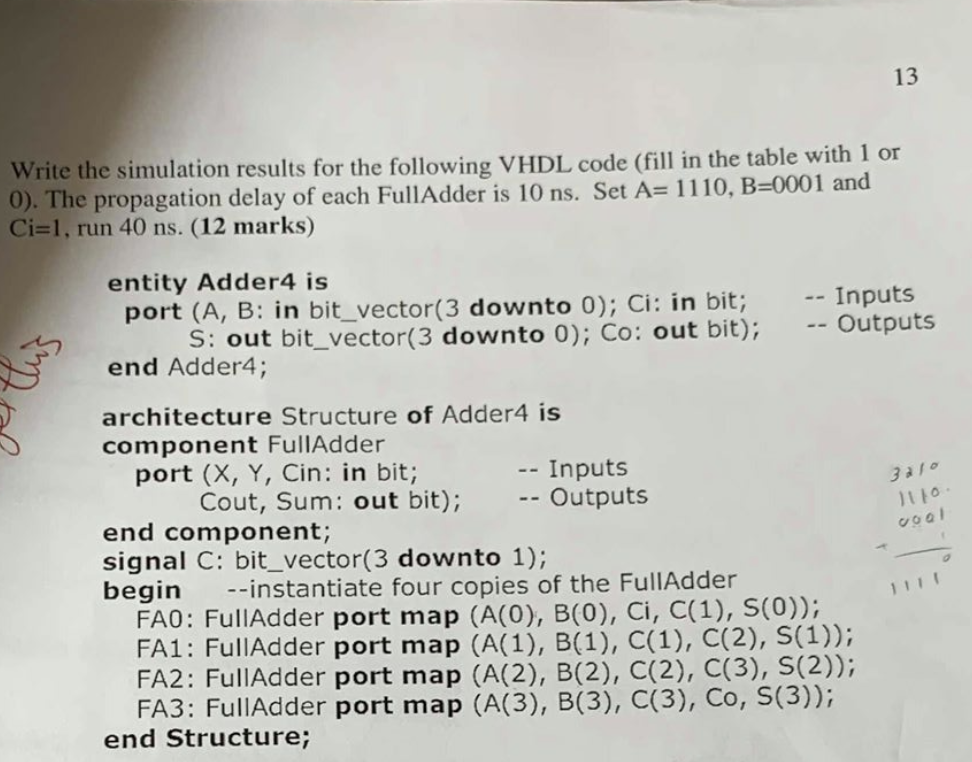

Write the simulation results for the following VHDL code (fill in the table with 1 or 0). The propagation delay of each FullAdder is 10 ns. Set A= 1110, B=0001 and Ci=1, run 40 ns. (12 marks) entity Adder4 is port (A, B: in bit_vector(3 downto 0); Ci: in bit; S: out bit_vector(3 downto 0); Co: out bit); end Adder4; -- Inputs -- Outputs 3210 vool architecture Structure of Adder4 is component FullAdder port (X, Y, Cin: in bit; -- Inputs Cout, Sum: out bit); -- Outputs end component; signal C: bit_vector(3 downto 1); begin --instantiate four copies of the FullAdder FAO: FullAdder port map (A(O), B(0), Ci, C(1), S(0)); FA1: FullAdder port map (A(1), B(1), C(1), C(2), S(1)); FA2: FullAdder port map (A(2), B(2), C(2), C(3), S(2)); FA3: FullAdder port map (A(3), B(3), C(3), Co, S(3)); end Structure; Write the simulation results for the following VHDL code (fill in the table with 1 or 0). The propagation delay of each FullAdder is 10 ns. Set A= 1110, B=0001 and Ci=1, run 40 ns. (12 marks) entity Adder4 is port (A, B: in bit_vector(3 downto 0); Ci: in bit; S: out bit_vector(3 downto 0); Co: out bit); end Adder4; -- Inputs -- Outputs 3210 vool architecture Structure of Adder4 is component FullAdder port (X, Y, Cin: in bit; -- Inputs Cout, Sum: out bit); -- Outputs end component; signal C: bit_vector(3 downto 1); begin --instantiate four copies of the FullAdder FAO: FullAdder port map (A(O), B(0), Ci, C(1), S(0)); FA1: FullAdder port map (A(1), B(1), C(1), C(2), S(1)); FA2: FullAdder port map (A(2), B(2), C(2), C(3), S(2)); FA3: FullAdder port map (A(3), B(3), C(3), Co, S(3)); end Structure

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts