Question: How would the multicycle MIPS design support the jr instruction? Show the machine code format and your solution should describe any new datapath features and

How would the multicycle MIPS design support the jr instruction? Show the machine code format and your solution should describe any new datapath features and control changes to the finite-state diagram below (this may include adding new states).

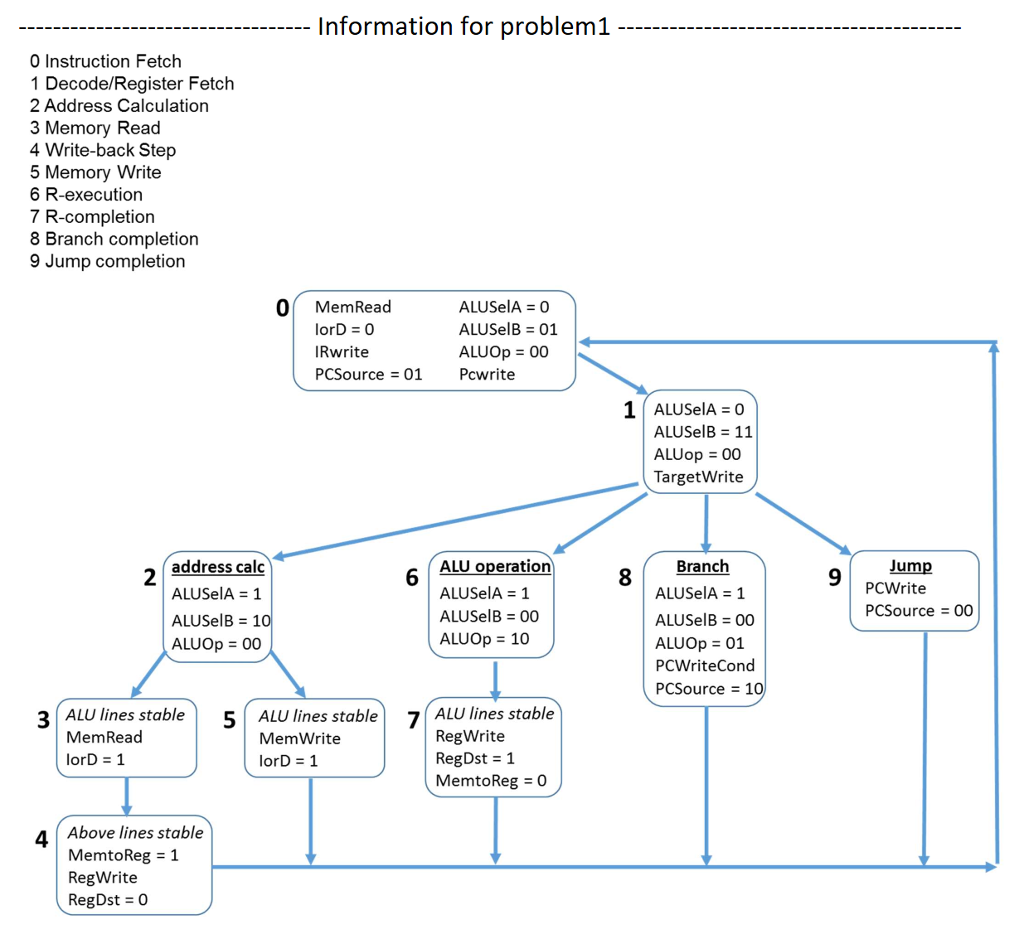

Information for problem1 0 Instruction Fetch 1 Decode/Register Fetch 2 Address Calculation 3 Memory Read 4 Write-back Step 5 Memory Write 6 R-execution 7 R-completion 8 Branch completion 9 Jump completion O Mem Read ALUSelA 0 ALUSelB 01 lorD 0 ALUOp 00 IR write PCSource 01 Powrite 1 ALUSeIA ALUSelB 11 ALUop 00 TargetWrite address calc ALU operation Branch ALUSeIA ALUSeIA ALUSelA 1 ALUSelB 00 ALUSelB 10 ALUSelB> 00 ALUop 10 ALUOp 01 ALUOp 00 PCWritecond PCSource 10 3 ALU lines stable 5 ALU lines stable 7 ALU lines stable MemRead RegWrite Mem Write RegDst 1 orD 1 lorD 1 MemtoReg O 4 Above lines stable MemtoReg 1 Reg Write RegDst O um PCWrite PC Source 00

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts