Question: I need help designing a circuit that detects 010 and 110 with overlap in the time trace provided. Design Specifications: Design a sequential system that

I need help designing a circuit that detects 010 and 110 with overlap in the time trace provided.

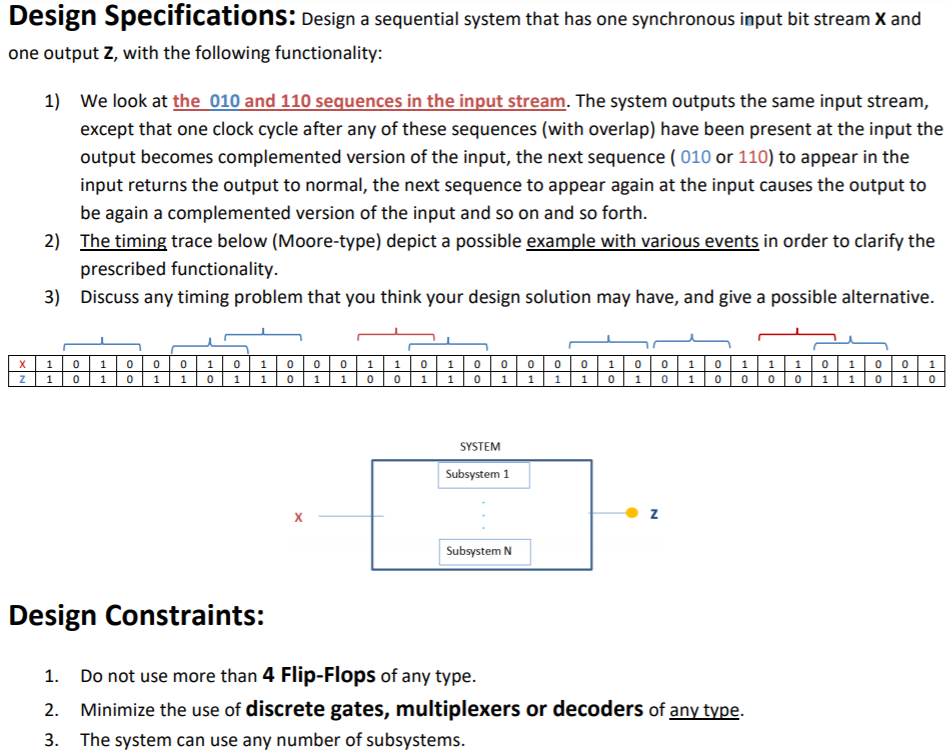

Design Specifications: Design a sequential system that has one synchronous input bit stream X and one output Z, with the following functionality: 1) We look at the 010 and 110 sequences in the input stream. The system outputs the same input stream, except that one clock cycle after any of these sequences (with overlap) have been present at the input the output becomes complemented version of the input, the next sequence (010 or 110) to appear in the input returns the output to normal, the next sequence to appear again at the input causes the output to be again a complemented version of the input and so on and so forth. 2) The timing trace below (Moore-type) depict a possible example with various events in order to clarify the prescribed functionality. 3) Discuss any timing problem that you think your design solution may have, and give a possible alternative. 0 1 0 0 x z 1 i o i o i 0 1 1 o 0 1 1 1 0 0 0 1 0 1 1 0 1 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 0 0 1 1 1 0 0 0 1 1 0 SYSTEM Subsystem 1 Subsystem N Design Constraints: 1. Do not use more than 4 Flip-Flops of any type. 2. Minimize the use of discrete gates, multiplexers or decoders of any type. 3. The system can use any number of subsystems. Design Specifications: Design a sequential system that has one synchronous input bit stream X and one output Z, with the following functionality: 1) We look at the 010 and 110 sequences in the input stream. The system outputs the same input stream, except that one clock cycle after any of these sequences (with overlap) have been present at the input the output becomes complemented version of the input, the next sequence (010 or 110) to appear in the input returns the output to normal, the next sequence to appear again at the input causes the output to be again a complemented version of the input and so on and so forth. 2) The timing trace below (Moore-type) depict a possible example with various events in order to clarify the prescribed functionality. 3) Discuss any timing problem that you think your design solution may have, and give a possible alternative. 0 1 0 0 x z 1 i o i o i 0 1 1 o 0 1 1 1 0 0 0 1 0 1 1 0 1 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 0 0 1 1 1 0 0 0 1 1 0 SYSTEM Subsystem 1 Subsystem N Design Constraints: 1. Do not use more than 4 Flip-Flops of any type. 2. Minimize the use of discrete gates, multiplexers or decoders of any type. 3. The system can use any number of subsystems

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts