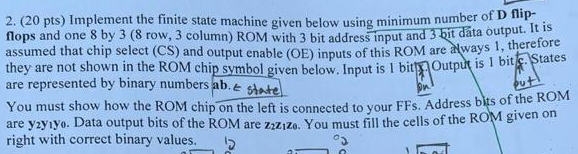

Question: Implement the finite state machine given below using minimum number of D flip - flops and one 8 by 3 ( 8 row, 3 column

Implement the finite state machine given below using minimum number of flip

flops and one by row, column ROM with bit address input and bit data output. It is

assumed that chip select CS and output enable OE inputs of this ROM are always therefore

they are not shown in the ROM chip symbol given below. Input is I bit output is bit States

are represented by binary numbers abt

You must show how the ROM chip on the left is connected to your FFs Address bits of the ROM

are Data output bits of the ROM are You must fill the cells of the ROM given on

right with correct binary values.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock