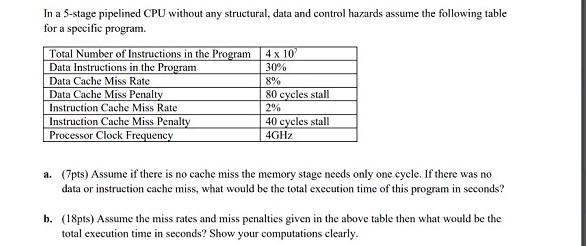

Question: In a 5-stage pipelined CPU without any structural, data and control hazards assume the following table for a specific program. Total Number of Instructions

In a 5-stage pipelined CPU without any structural, data and control hazards assume the following table for a specific program. Total Number of Instructions in the Program 4 x 10 30% Data Instructions in the Program Data Cache Miss Rate Data Cache Miss Penalty Instruction Cache Miss Rate Instruction Cache Miss Penalty Processor Clock Frequency 8% 80 cycles stall 2% 40 cycles stall 4GHz a. (7pts) Assume if there is no cache miss the memory stage needs only one cycle. If there was no data or instruction cache miss, what would be the total execution time of this program in seconds? b. (18pts) Assume the miss rates and miss penalties given in the above table then what would be the total execution time in seconds? Show your computations clearly.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts