Question: In a single-cycle processor, the instruction memory iMen is 3232-bit, the register file rFile is 3232-bit, data memory dMem is 3232-bit, and the program counter

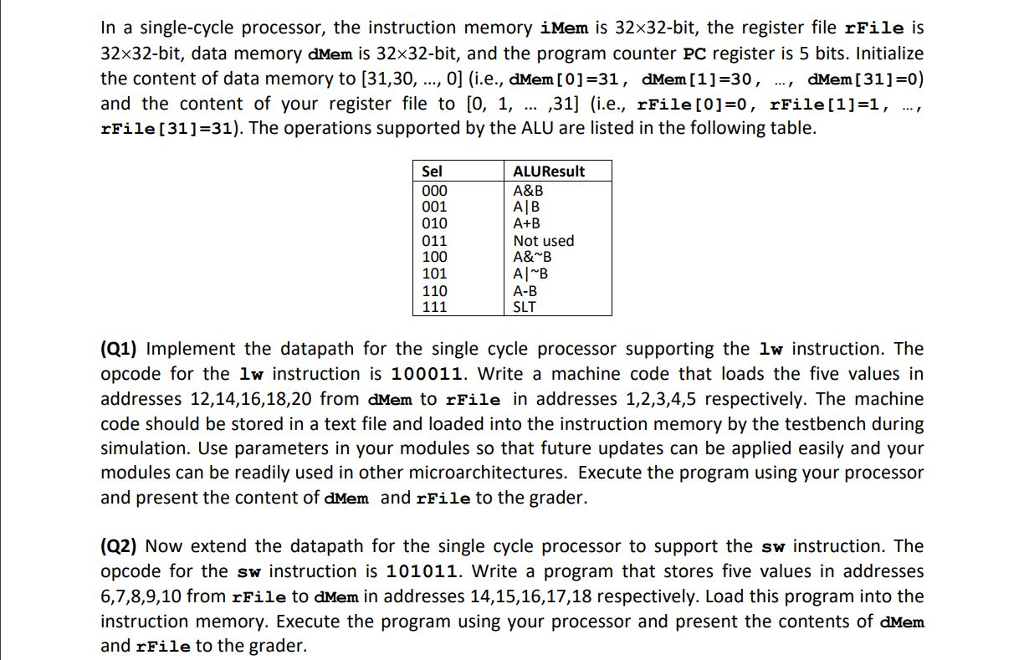

In a single-cycle processor, the instruction memory iMen is 3232-bit, the register file rFile is 3232-bit, data memory dMem is 3232-bit, and the program counter PC register is 5 bits. Initialize the content of data memory to [31,30, ..., 0] (i.e., dMem[0] 31, dMem [1] 30, .., dMem [31] 0) and the content of your register file to [0, 1, ,31] (i.e., rFile [0]-0, rFile[1]-1, ..., rFile[31]-31). The operations supported by the ALU are listed in the following table. ALUResult A&B A|B A+B Not used A& B Sel 001 010 011 100 101 110 A-B SLT (Q1) Implement the datapath for the single cycle processor supporting the lw instruction. The opcode for the lw instruction is 100011. Write a machine code that loads the five values in addresses 12,14,16,18,20 from dMem to rFile in addresses 1,2,3,4,5 respectively. The machine code should be stored in a text file and loaded into the instruction memory by the testbench during simulation. Use parameters in your modules so that future updates can be applied easily and your modules can be readily used in other microarchitectures. Execute the program using your processor and present the content of dMem and rFile to the grader. (Q2) Now extend the datapath for the single cycle processor to support the sw instruction. The opcode for the sw instruction is 101011. Write a program that stores five values in addresses 6,7,8,9,10 from rFile to dMem in addresses 14,15,16,17,18 respectively. Load this program into the instruction memory. Execute the program using your processor and present the contents of dMem and rFile to the grader

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts