Question: In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this exercise assume that individual stages of the

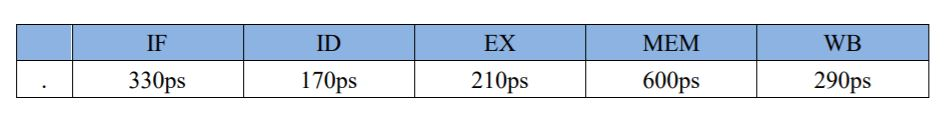

In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this exercise assume that individual stages of the datapath have the following latencies:

. Consider that the pipeline register delay is 20ps. If the pipelined machine had an infinite number of stages, what would its speedup be over the single-cycle machine?

WB EX MEM IF ID 210ps 600ps 290ps 330ps 170ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts