Question: In Verilog 2-1. Design a sequence detector implementing a Moore state machine using three always blocks. The Moore state machine has two inputs (ain[1:0]) and

In Verilog

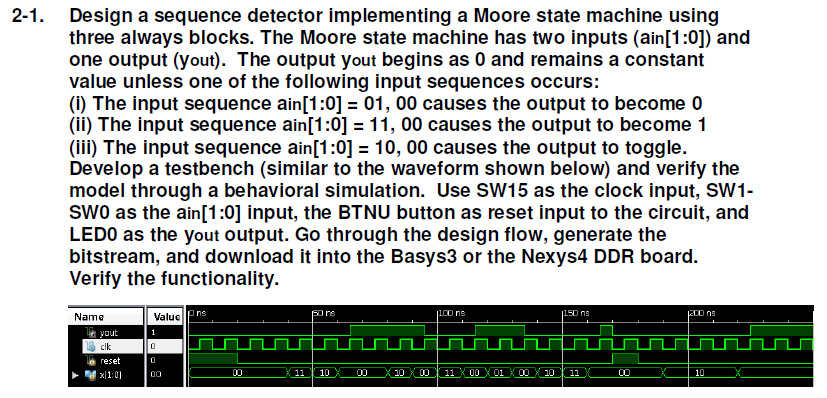

2-1. Design a sequence detector implementing a Moore state machine using three always blocks. The Moore state machine has two inputs (ain[1:0]) and one output (Yout). The output yout begins as 0 and remains a constant value unless one of the following input sequences occurs: (i) The input sequence ain[1:0] = 01, 00 causes the output to become 0 (ii) The input sequence ain[1:0] = 11,00 causes the output to become 1 (iii) The input sequence ain[1:0] = 10,00 causes the output to toggle. Develop a testbench (similar to the waveform shown below) and verify the model through a behavioral simulation. Use SW15 as the clock input, SW1- SWO as the ain[1:0] input, the BTNU button as reset input to the circuit, and LEDO as the yout output. Go through the design flow, generate the bitstream, and download it into the Basys3 or the Nexys4 DDR board. Verify the functionality. Bure Valus pne 100 ns L200 NS 1 Name yout clk reset x(1:0) 00 00 1110 10 X 0011 00 01. 10 11 00 10

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts