Question: in VHDL Design a fully connected 33 reconfigurable computing architecture where each computational unit (CU) in a row can send information to any of the

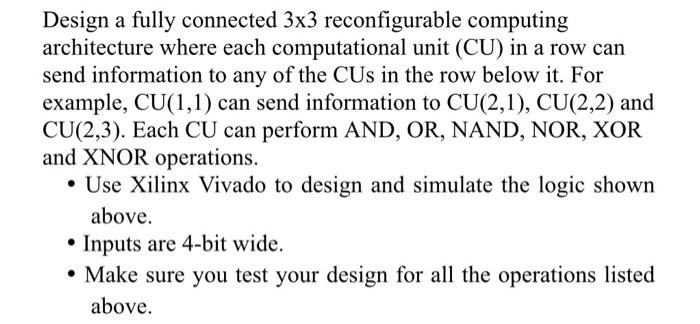

Design a fully connected 33 reconfigurable computing architecture where each computational unit (CU) in a row can send information to any of the CUs in the row below it. For example, CU(1,1) can send information to CU(2,1),CU(2,2) and CU(2,3). Each CU can perform AND, OR, NAND, NOR, XOR and XNOR operations. - Use Xilinx Vivado to design and simulate the logic shown above. - Inputs are 4-bit wide. - Make sure you test your design for all the operations listed above

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts