Question: Please Solve for question 2 Using Intel Quartus, implement the combination logic circuits in VHDL. When asked, provided the manual solution. Instructions: - Group: up

Please Solve for question 2

Please Solve for question 2

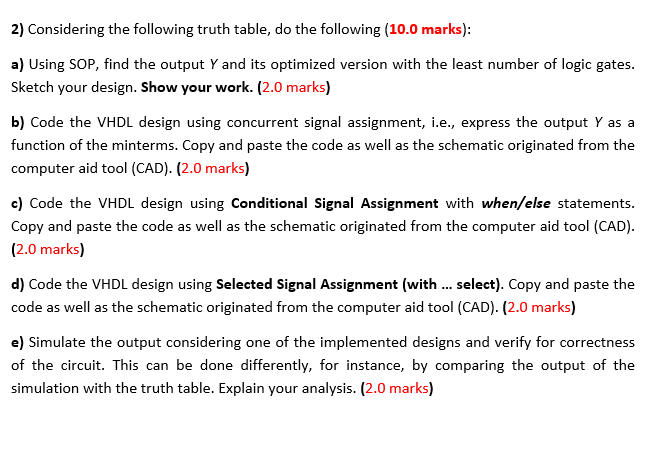

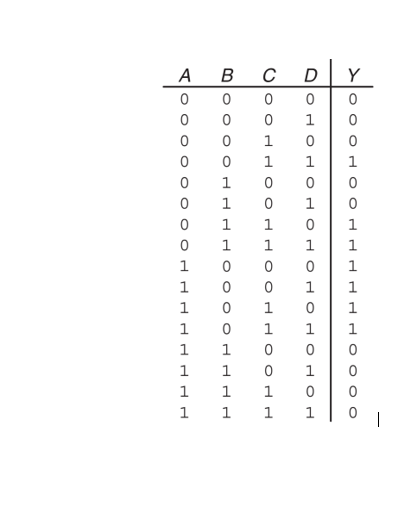

Using Intel Quartus, implement the combination logic circuits in VHDL. When asked, provided the manual solution. Instructions: - Group: up to 3 students. - Use this document to write the solutions. Group information must be populated in Section C - Use ".PDF to report your assignment. Any other format will lead to a point deduction of 3.0 mark. 2) Considering the following truth table, do the following (10.0 marks): a) Using SOP, find the output Y and its optimized version with the least number of logic gates. Sketch your design. Show your work. (2.0 marks) b) Code the VHDL design using concurrent signal assignment, i.e., express the output Y as a function of the minterms. Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). ( 2.0 marks) c) Code the VHDL design using Conditional Signal Assignment with when/else statements. Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). (2.0 marks) d) Code the VHDL design using Selected Signal Assignment (with ... select). Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). (2.0 marks) e) Simulate the output considering one of the implemented designs and verify for correctness of the circuit. This can be done differently, for instance, by comparing the output of the simulation with the truth table. Explain your analysis. (2.0 marks) \begin{tabular}{cccc|c} A & B & C & D & Y \\ \hline 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 \\ & & & & \end{tabular} Using Intel Quartus, implement the combination logic circuits in VHDL. When asked, provided the manual solution. Instructions: - Group: up to 3 students. - Use this document to write the solutions. Group information must be populated in Section C - Use ".PDF to report your assignment. Any other format will lead to a point deduction of 3.0 mark. 2) Considering the following truth table, do the following (10.0 marks): a) Using SOP, find the output Y and its optimized version with the least number of logic gates. Sketch your design. Show your work. (2.0 marks) b) Code the VHDL design using concurrent signal assignment, i.e., express the output Y as a function of the minterms. Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). ( 2.0 marks) c) Code the VHDL design using Conditional Signal Assignment with when/else statements. Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). (2.0 marks) d) Code the VHDL design using Selected Signal Assignment (with ... select). Copy and paste the code as well as the schematic originated from the computer aid tool (CAD). (2.0 marks) e) Simulate the output considering one of the implemented designs and verify for correctness of the circuit. This can be done differently, for instance, by comparing the output of the simulation with the truth table. Explain your analysis. (2.0 marks) \begin{tabular}{cccc|c} A & B & C & D & Y \\ \hline 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 \\ & & & & \end{tabular}

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts