Question: Instruction Pipelining w / and w / o the Bypass Circuit: Show the execution of the following sequence of MIPS instructions on the pipeline diagrams.

Instruction Pipelining w and wo the Bypass Circuit:

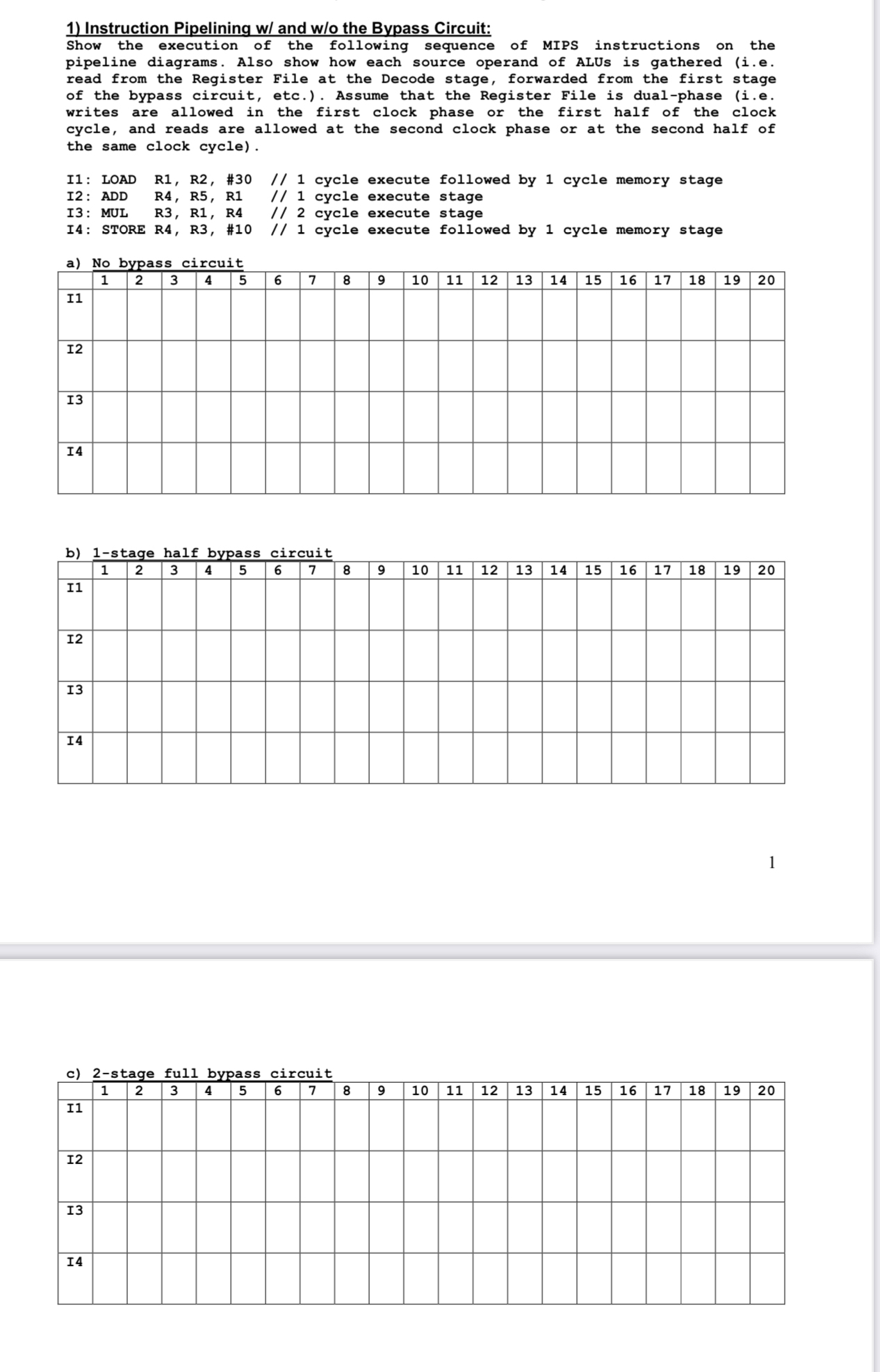

Show the execution of the following sequence of MIPS instructions on the pipeline diagrams. Also show how each source operand of ALUs is gathered ie read from the Register File at the Decode stage, forwarded from the first stage of the bypass circuit, etc. Assume that the Register File is dualphase ie writes are allowed in the first clock phase or the first half of the clock cycle, and reads are allowed at the second clock phase or at the second half of the same clock cycle

I: LOAD R R # cycle execute followed by cycle memory stage

I: ADD R R R cycle execute stage

I: MUL R R R cycle execute stage

I: STORE R R # cycle execute followed by cycle memory stage

a No bypass circuit

tableII

bstage half bypass circuit

tableII

cstage full bypass circuit

tableI

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock