Question: Just as it's helpful to define intermediate variables in a software program, it is often useful to define intermediate signals to represent part of

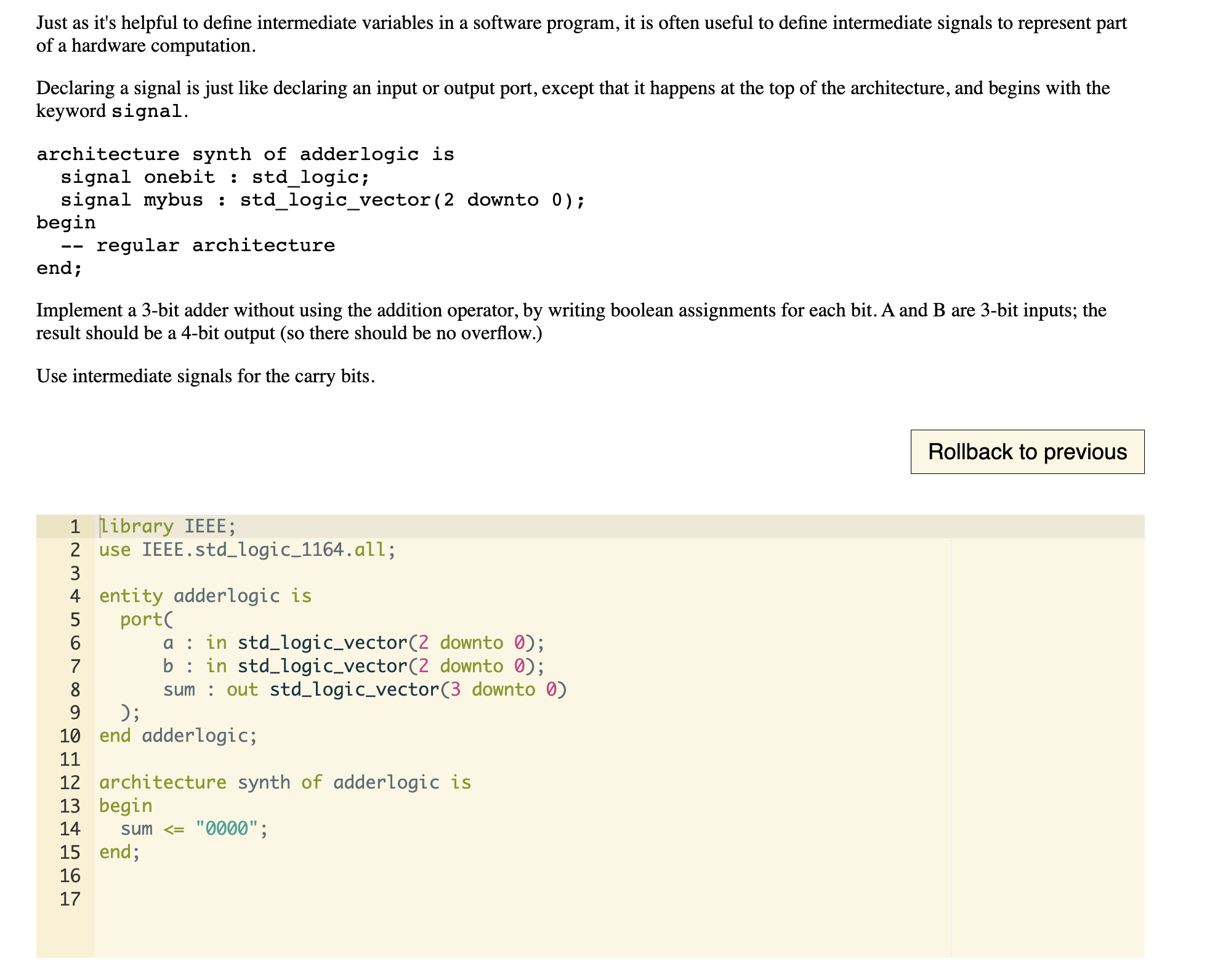

Just as it's helpful to define intermediate variables in a software program, it is often useful to define intermediate signals to represent part of a hardware computation. Declaring a signal is just like declaring an input or output port, except that it happens at the top of the architecture, and begins with the keyword signal. architecture synth of adderlogic is signal onebit : std_logic; signal mybus : std_logic_vector(2 downto 0); begin end; regular architecture Implement a 3-bit adder without using the addition operator, by writing boolean assignments for each bit. A and B are 3-bit inputs; the result should be a 4-bit output (so there should be no overflow.) Use intermediate signals for the carry bits. 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 4 5 port( 6 7 8 9 ); 10 end adderlogic; 11 12 architecture synth of adderlogic is 13 begin 14 sum

Step by Step Solution

3.24 Rating (153 Votes )

There are 3 Steps involved in it

The question asks for the implementation of a 3bit adder with a 4bit output in VHDL without using th... View full answer

Get step-by-step solutions from verified subject matter experts