Question: Lab logic Given the following module definitions for l-bit Full Adder and 2-input XOR gate and 2-input AND gate: module One_Bit_FA (X,Y,Z, Cout,s); input X,Y,Z;

Lab logic

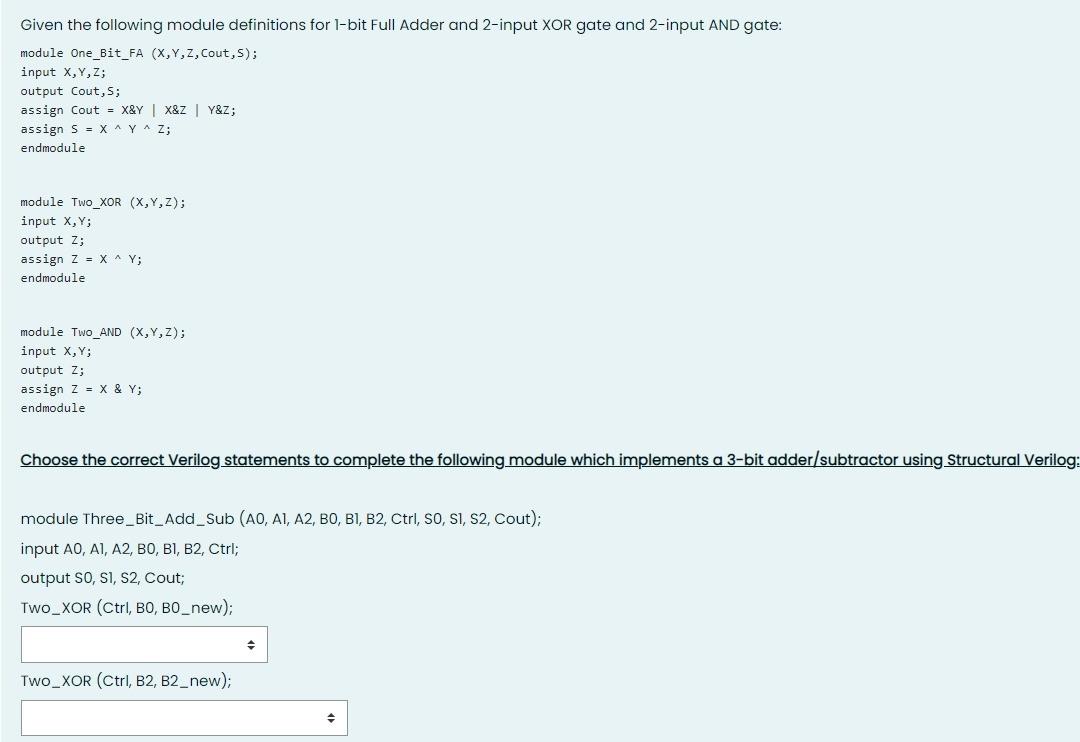

Given the following module definitions for l-bit Full Adder and 2-input XOR gate and 2-input AND gate: module One_Bit_FA (X,Y,Z, Cout,s); input X,Y,Z; output Cout,S; assign Cout = X&Y | X&Z | Y&z; assign S = X - Y - Z; endmodule module Two_XOR (X,Y,Z); input X,Y; output z; assign Z = XAY; endmodule module Two_AND (X,Y,Z); input X, Y; output z; assign Z = X & Y; endmodule Choose the correct Verilog statements to complete the following module which implements a 3-bit adder/subtractor using Structural Verilog: module Three_Bit_Add_Sub (AO, A1, A2, BO, BI, B2, Ctrl, SO, S1, S2, Cout); input A0, A1, A2, BO, BI, B2, Ctrl; output SO, SI, S2, Cout; TWO_XOR (Ctrl, BO, BO_new); TWO_XOR (Ctrl, B2, B2_new)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts