Question: Layout an N x N array multiplier in a given area (approximately 0.8 mm 2 ). The following are the design requirements and objectives: 1.

Layout an N x N array multiplier in a given area (approximately 0.8mm2). The following are the design requirements and objectives:

1. Implement a rectangular layout. 2. The inputs X and Y are fed serially to the multiplier. 3. Both X and Y should be registered. 4. You need to maximize N. 5. Product P should be registered and clocked out serially. 6. The three registers are clocked by an external clock signal.

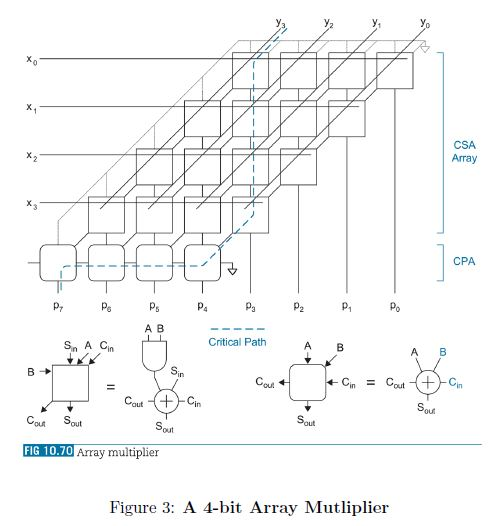

CSA Array CPA P1 A B Critical Path A B Sin CotCn Cou Sout ut out FIG 10.70 Array multiplier Figure 3: A 4-bit Array Mutliplier CSA Array CPA P1 A B Critical Path A B Sin CotCn Cou Sout ut out FIG 10.70 Array multiplier Figure 3: A 4-bit Array Mutliplier

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts