Question: MIPS code question Given the following MIPS code: If we run it on a five-stage pipelined M.I.P.S. processor (with data-forwarding when possible to handle hazards).

MIPS code question

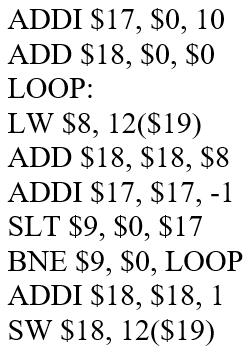

Given the following MIPS code:

If we run it on a five-stage pipelined M.I.P.S. processor (with data-forwarding when possible to handle hazards). No branch hazard reduction techniques are used here

a) Identify the instructions that will be in the pipeline, and at which stages, and when is the 1st time the codes decided to take a branch?

b) What will cause your code to need to flush instructions from the pipeline, how many times will this occur, and which instructions will need to be flushed each time?

c) If the cycle time is 11 ns, how long will it take to run all lines of your MIPS assembly code (including all iterations of the looping code, stalls, and flushing) on this pipelined processor? Explain your answer

d) when running the MIPS code, what is the speedup of: - the multi-cycle processor over the single-cycle processor? - the pipelined processor over the multi-cycle processor?

ADDI $17, $0, 10 ADD $18, $0, $0 LOOP: LW $8, 12($19) ADD $18, $18, $8 ADDI $17, $17, -1 SLT $9, $0, $17 BNE $9, $0, LOOP ADDI $18, $18, 1 SW $18, 12($19) ADDI $17, $0, 10 ADD $18, $0, $0 LOOP: LW $8, 12($19) ADD $18, $18, $8 ADDI $17, $17, -1 SLT $9, $0, $17 BNE $9, $0, LOOP ADDI $18, $18, 1 SW $18, 12($19)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts