Question: MIPS Data Path Code analysis Rewrite the code using a minimum number of nop instructions to eliminate hazards. You can reorder the instructions assuming that

MIPS Data Path Code analysis

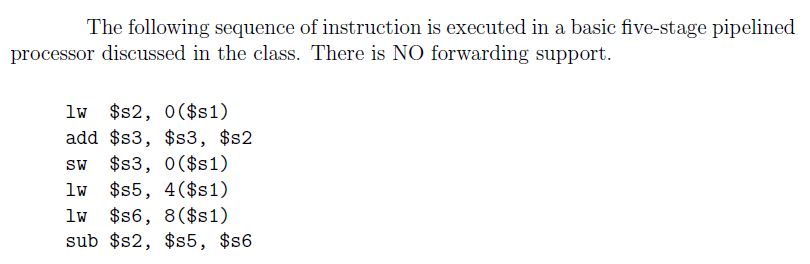

Rewrite the code using a minimum number of nop instructions to eliminate hazards. You can reorder the instructions assuming that register read and write at the same address can happen in one clock cycle. And explain why or why not branch prediction could help eliminate the hazards in the code?

The following sequence of instruction is executed in a basic five-stage pipelined processor discussed in the class. There is NO forwarding support lw $s2, 0 ($s1) add $s3, $s3, $s2 SW $s3, 0 ($s1) lw $s5, 4($s1) lw $s6, 8 ($s1) sub $s2, $s5, $s6

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts