Question: modify following verilog code as required . . . . Project Description This project involves modeling and implementing a Smart Parking System circuit with the

modify following verilog code as required

Project Description

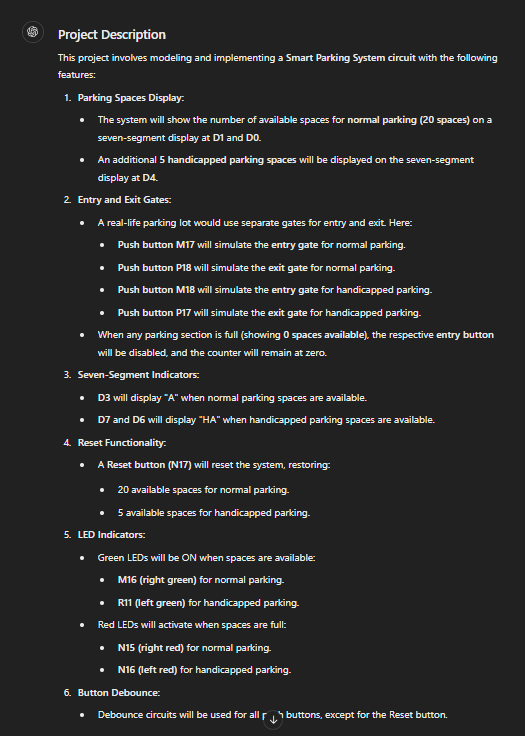

This project involves modeling and implementing a Smart Parking System circuit with the following

features:

Parking Spaces Display:

The system will show the number of available spaces for normal parking spaces on a

sevensegment display at D and D

An additional handicapped parking spaces will be displayed on the sevensegment

display at D

Entry and Exit Gates:

A reallife parking lot would use separate gates for entry and exit. Here:

Push button M will simulate the entry gate for normal parking.

Push button P will simulate the exit gate for normal parking.

Push button M will simulate the entry gate for handicapped parking.

Push button P will simulate the exit gate for handicapped parking.

When any parking section is full showing spaces available the respective entry button

will be disabled, and the counter will remain at zero.

SevenSegment Indicators:

D will display A when normal parking spaces are available.

D and D will display HA when handicapped parking spaces are available.

Reset Functionality:

A Reset button N will reset the system, restoring:

available spaces for normal parking.

available spaces for handicapped parking.

LED Indicators:

Green LEDs will be ON when spaces are available:

Mright green for normal parking.

Rleft green for handicapped parking.

Red LEDs will activate when spaces are full:

Nright red for normal parking.

Nleft red for handicapped parking.

Button Debounce:

Debounce circuits will be used for all rdarrh buttons, except for the Reset button.Key Requirements

Simulation:

Accurate simulation is critical to validate the correctness of the code and circuit design. Simulations should be provided for all modules implemented.

Design Specifications:

Use or modify existing modules from previous experiments where applicable.Design additional modules as needed.

Circuit Efficiency:

The design should prioritize efficient use of FPGA resources, such as lookup tables LUTs registers, and IOBs.the code:module SmartParkingSystem

input clk reset,

input btnentrynorm, btnexitnorm,

input btnentryhand, btnexithand,

output : segnorm, :seghand,

output : an

output lednormgreen, ledhandgreen,

output lednormred, ledhandred

;

wire debounceentrynorm, debounceexitnorm;

wire debounceentryhand, debounceexithand;

wire : normspaces, handspaces;

wire normfull, handfull;

Debouncing

Debounce dbclk btnentrynorm, debounceentrynorm;

Debounce dbclk btnexitnorm, debounceexitnorm;

Debounce dbclk btnentryhand, debounceentryhand;

Debounce dbclk btnexithand, debounceexithand;

Parking Counters

ParkingCounter normcounter

clk reset, debounceentrynorm, debounceexitnorm,

d normspaces, normfull

;

ParkingCounter handcounter

clk reset, debounceentryhand, debounceexithand,

d handspaces, handfull

;

SevenSegment Display

SevenSegmentDriver normdisplaynormspaces, segnorm;

SevenSegmentDriver handdisplayhandspaces, seghand;

LED Control

assign lednormgreen ~normfull;

assign lednormred normfull;

assign ledhandgreen ~handfull;

assign ledhandred handfull;

Display Control

assign an b; Modify for multiplexing if required

endmodule;module Debounce

input clk

input btnin

output reg btnout

;

reg : count;

reg btnstate;

always @posedge clk begin

if btnin btnstate begin

count count ;

if count hFFFFF begin

btnstate btnin;

count ;

end

end else begin

count ;

end

end

always @posedge clk

btnout btnstate;

endmodule;module ParkingCounter

input clk

input reset,

input entry,

input exit,

input : maxspaces,

output reg : spaces,

output reg full

;

always @posedge clk or posedge reset begin

if reset

spaces maxspaces;

else if entry && spaces

spaces spaces ;

else if exit && spaces maxspaces

spaces spaces ;

end

always @ begin

full spaces ;

end

endmodule;module SevenSegmentDriver

input : digit,

output reg : seg

;

always @ begin

case digit

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

d: seg b;

default: seg b;

endcase

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock