Question: Module coUNT is a 3-bit binary up-counter with parallel load. While load =0 , counter increases by 1 each time a positive edge of clk

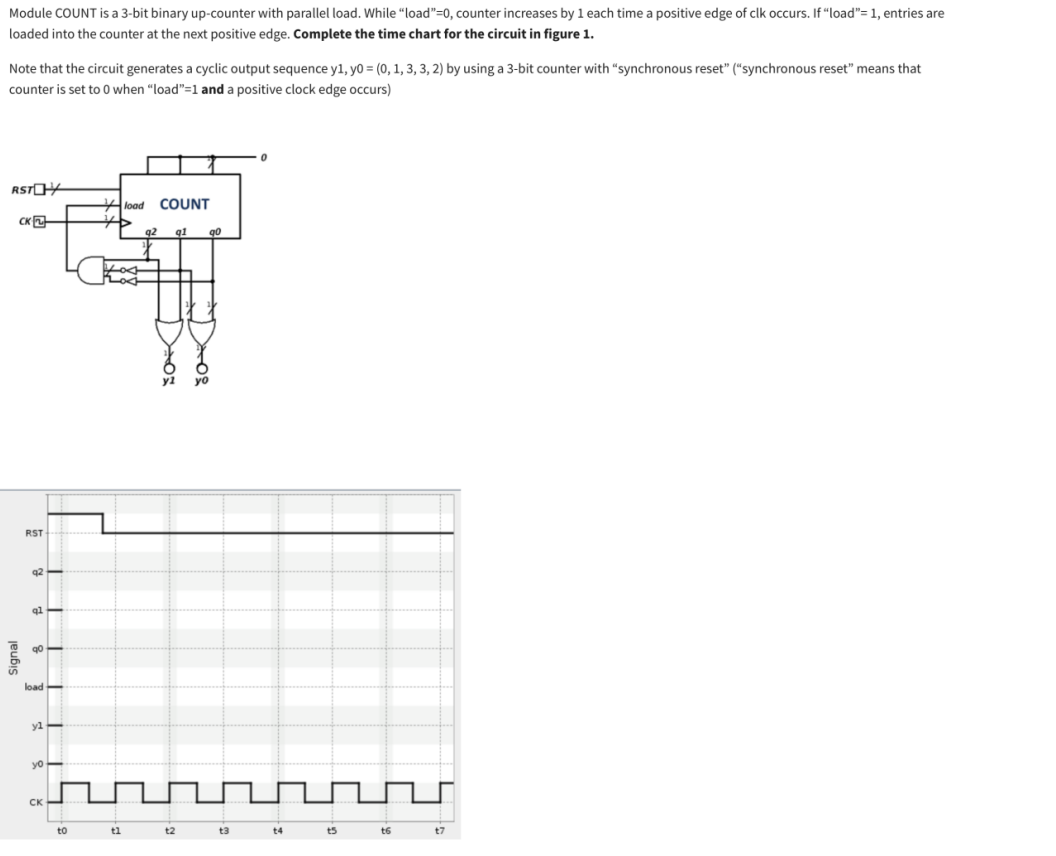

Module coUNT is a 3-bit binary up-counter with parallel load. While "load"

=0, counter increases by 1 each time a positive edge of clk occurs. If "load"

=1, entries are\ loaded into the counter at the next positive edge. Complete the time chart for the circuit in figure 1.\ Note that the circuit generates a cyclic output sequence y1, y0

=(0,1,3,3,2)by using a 3-bit counter with "synchronous reset" ("synchronous reset" means that\ counter is set to 0 when "load"

=1and a positive clock edge occurs) NOTE: Please draw the circuit by hand, thank you so much!

Module COUNT is a 3-bit binary up-counter with parallel load. While "load" =0, counter increases by 1 each time a positive edge of clk occurs. If "load" =1, entries are loaded into the counter at the next positive edge. Complete the time chart for the circuit in figure 1. Note that the circuit generates a cyclic output sequence y1,y0=(0,1,3,3,2) by using a 3-bit counter with "synchronous reset" "synchronous reset" means that counter is set to 0 when "load" =1 and a positive clock edge occurs)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts