Question: N.B: Coding for this task must be done by using the software 'Vivado' The 7 Segment Display Driver Introduction The aim of this task 2

N.B: Coding for this task must be done by using the software 'Vivado'

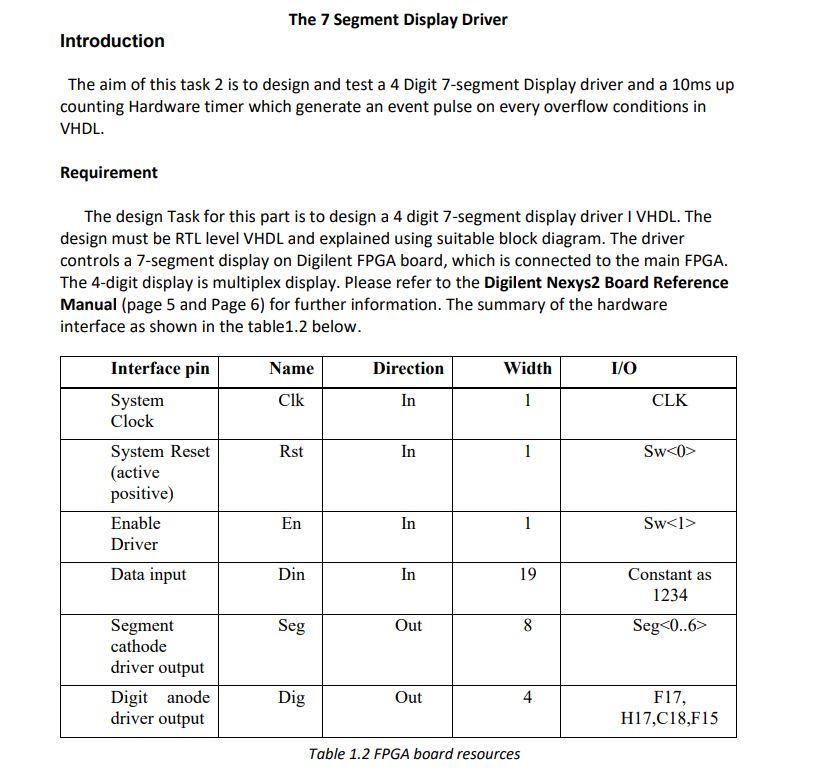

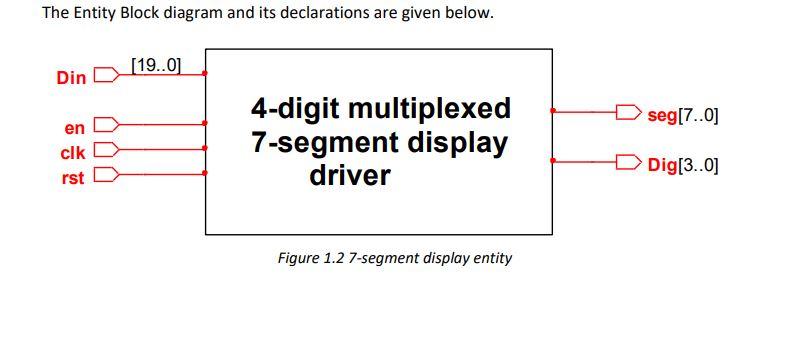

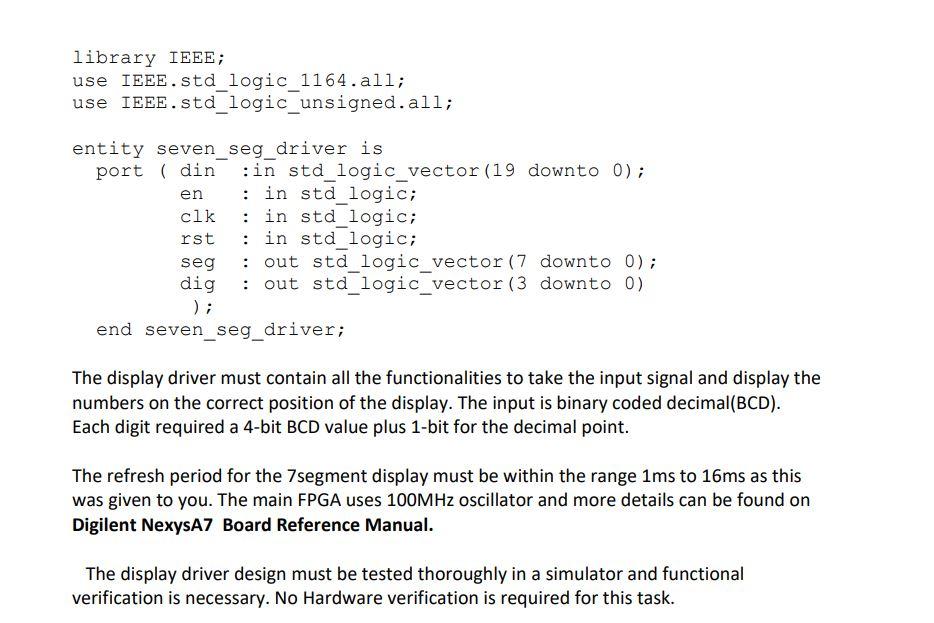

The 7 Segment Display Driver Introduction The aim of this task 2 is to design and test a 4 Digit 7-segment Display driver and a 10ms up counting Hardware timer which generate an event pulse on every overflow conditions in VHDL. Requirement The design Task for this part is to design a 4 digit 7-segment display driver I VHDL. The design must be RTL level VHDL and explained using suitable block diagram. The driver controls a 7-segment display on Digilent FPGA board, which is connected to the main FPGA. The 4-digit display is multiplex display. Please refer to the Digilent Nexys2 Board Reference Manual (page 5 and Page 6) for further information. The summary of the hardware interface as shown in the table1.2 below. Name Direction Width I/O Clk In 1 CLK Rst In Sw

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts