Question: NEED HELP! processor X has the following cache configuration: Memory addressing bit: 30 bits Cache size: 128K Byte Block size: 32 Byte Mapping: 2-way associative

NEED HELP!

NEED HELP!

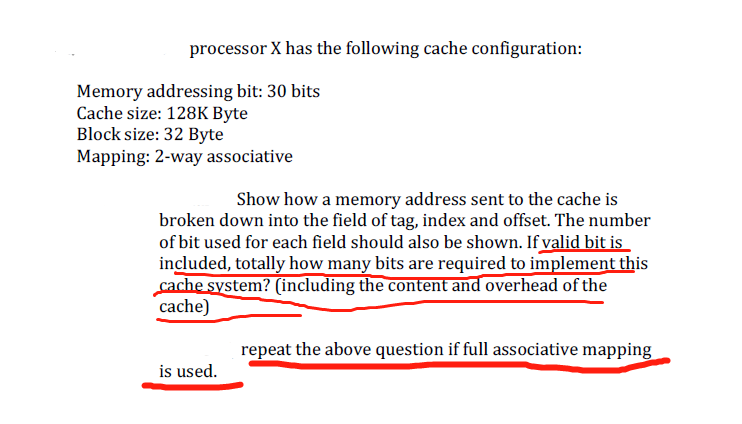

processor X has the following cache configuration: Memory addressing bit: 30 bits Cache size: 128K Byte Block size: 32 Byte Mapping: 2-way associative Show how a memory address sent to the cache is broken down into the field of tag, index and offset. The number of bit used for each field should also be shown. If valid bit is included, totally how many bits are required to implement this ache svstem? (including the content and overhead of the cache) repeat the above question if full associative mapping is used. processor X has the following cache configuration: Memory addressing bit: 30 bits Cache size: 128K Byte Block size: 32 Byte Mapping: 2-way associative Show how a memory address sent to the cache is broken down into the field of tag, index and offset. The number of bit used for each field should also be shown. If valid bit is included, totally how many bits are required to implement this ache svstem? (including the content and overhead of the cache) repeat the above question if full associative mapping is used

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts