Question: NOTE TO EXPERTS: PLEASE DON'T ATTEMPT THIS QUESTION IF YOU ARE NOT EXPERT AT MIPS ASSEMBLY LANGUAGE The coprocessor 0 in a MIPS processor has

NOTE TO EXPERTS: PLEASE DON'T ATTEMPT THIS QUESTION IF YOU ARE NOT EXPERT AT MIPS ASSEMBLY LANGUAGE

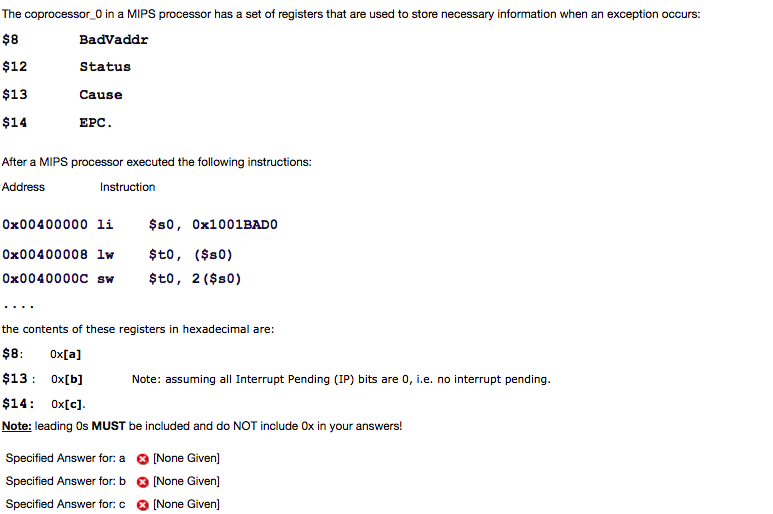

The coprocessor 0 in a MIPS processor has a set of registers that are used to store necessary information when an exception occurs: $8 $12 $13 $14 BadVaddr Status Cause EPC After a MIPS processor executed the following instructions: Address Instruction ox00400000 1i $s0, 0x1001BADO 0x00400008 1w $t0, ($s0) 0x0040000C sw $t0, 2 ($s0) the contents of these registers in hexadecimal are: $8 x[a] $13: 0x[b] $14: 0x[c] Note: leading Os MUST be included and do NOT include 0x in your answers! Specified Answer for aNone Given] Specified Answer forbNone Given] Specified Answ forcNone Given] Note: assuming all Interrupt Pending (IP) bits are 0, i.e. no interrupt pending The coprocessor 0 in a MIPS processor has a set of registers that are used to store necessary information when an exception occurs: $8 $12 $13 $14 BadVaddr Status Cause EPC After a MIPS processor executed the following instructions: Address Instruction ox00400000 1i $s0, 0x1001BADO 0x00400008 1w $t0, ($s0) 0x0040000C sw $t0, 2 ($s0) the contents of these registers in hexadecimal are: $8 x[a] $13: 0x[b] $14: 0x[c] Note: leading Os MUST be included and do NOT include 0x in your answers! Specified Answer for aNone Given] Specified Answer forbNone Given] Specified Answ forcNone Given] Note: assuming all Interrupt Pending (IP) bits are 0, i.e. no interrupt pending

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts