Question: Part III - Analysis In a single-core CPU that has a five-stage pipeline, it takes 1 CPU clock cycle to fetch the instruction, 1 CPU

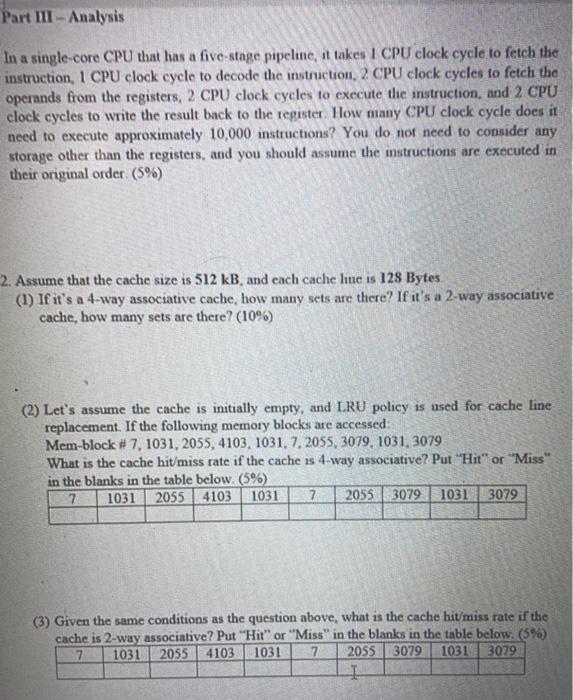

Part III - Analysis In a single-core CPU that has a five-stage pipeline, it takes 1 CPU clock cycle to fetch the instruction, 1 CPU clock cycle to decode the instruction, 2 CPU clock cycles to fetch the operands from the registers, 2 CPU clock cycles to execute the instruction, and 2 CPU clock cycles to write the result back to the register How many CPU clock cycle does it need to execute approximately 10,000 instructions? You do not need to consider any storage other than the registers, and you should assume the instructions are executed in their original order (59) 2. Assume that the cache size is 512 kB, and each cache line is 128 Bytes (1) If it's a 4-way associative cache, how many sets are there? If it's a 2-way associative cache, how many sets are there? (10%) (2) Let's assume the cache is initially empty, and LRU policy is used for cache line replacement. If the following memory blocks are accessed Mem-block # 7, 1031, 2055, 4103, 1031.7.2055, 3079, 1031, 3079 What is the cache hit/miss rate if the cache is 4-way associative? Put "Hit" or "Miss" in the blanks in the table below. (5%) 7 1031 2055 4103 1031 7 2055.3079 1031 3079 (3) Given the same conditions as the question above, what is the cache hit/miss rate if the cache is 2-way associative? Put "Hit" or "Miss" in the blanks in the table below. (5%) 1031 20554103 1031 7. 20553079 1031 3079

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts