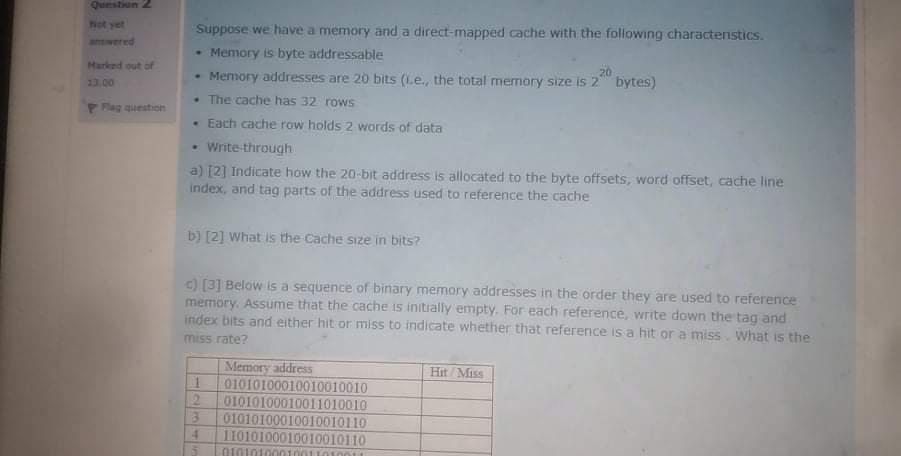

Question: Plaquestion Suppose we have a memory and a direct-mapped cache with the following charactenstics. Memory is byte addressable 20 Memory addresses are 20 bits (le,

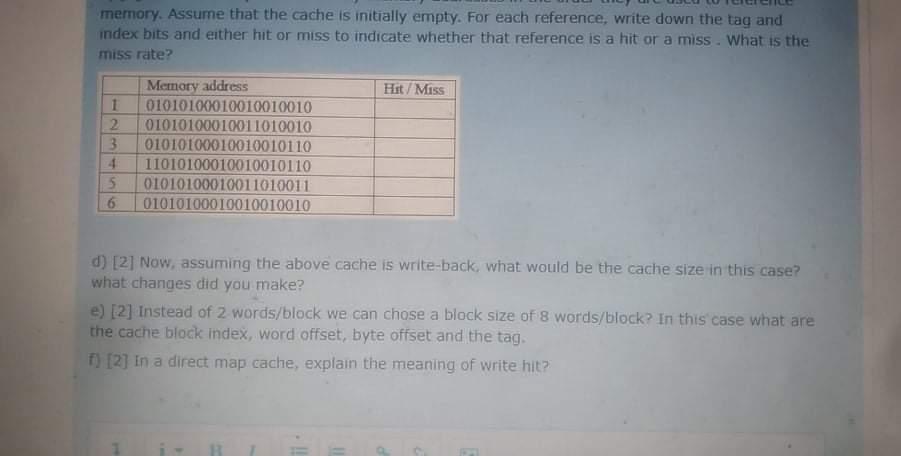

Plaquestion Suppose we have a memory and a direct-mapped cache with the following charactenstics. Memory is byte addressable 20 Memory addresses are 20 bits (le, the total memory size is 2 bytes) The cache has 32 rows Each cache row holds 2 words of data Write through a) [2] Indicate how the 20-bit address is allocated to the byte offsets, word offset, cache line Index, and tag parts of the address used to reference the cache b) [2] What is the Cache size in bits? c) [3] Below is a sequence of binary memory addresses in the order they are used to reference memory. Assume that the cache is initially empty. For each reference, write down the tag and index bits and either hit or miss to indicate whether that reference is a hit or a miss what is the miss rate? Memory address Fit Miss 01010100010010010010 2 01010100010011010010 01010100010010010110 T1010100010010010110 OOOO memory. Assume that the cache is initially empty. For each reference, write down the tag and index bits and either hit or miss to indicate whether that reference is a hit or a miss. What is the miss rate? Hit/Miss 1 2 3 4 5 6 Memory address 01010100010010010010 01010100010011010010 01010100010010010110 11010100010010010110 01010100010011010011 01010100010010010010 d) [2] Now, assuming the above cache is write-back, what would be the cache size in this case? what changes did you make? e) [2] Instead of 2 words/block we can chose a block size of 8 words/block? In this case what are the cache block index, word offset, byte offset and the tag. f) [2] In a direct map cache, explain the meaning of write hit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts