Question: Please explain in details: 1 - Consider the following code describing a combinational logic: module DUT ( A , B , C , S ,

Please explain in details:

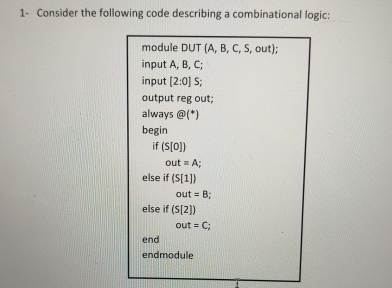

Consider the following code describing a combinational logic:

module DUT A B C S out;

input A B C;

input : S;

output reg out;

always @

begin

if S

out A;

else if S

out B;

else if S

out C;

end

endmodule

a Draw the synthesized circuit out of the above code. What is the possible problem with this design?

b Proposed two solutions to resolve this problem along with their synthesized circuits.

c Implement the modified design in part b using tristate buffers without using multiplexers. Show your architecture and RTL code.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock