Question: Please explain the code line by line 3. Implement a 3-bit binary down counter (VHDL). -- VHDL Code for 3-bit binary down counter #Implementation Constraint

Please explain the code line by line

Please explain the code line by line

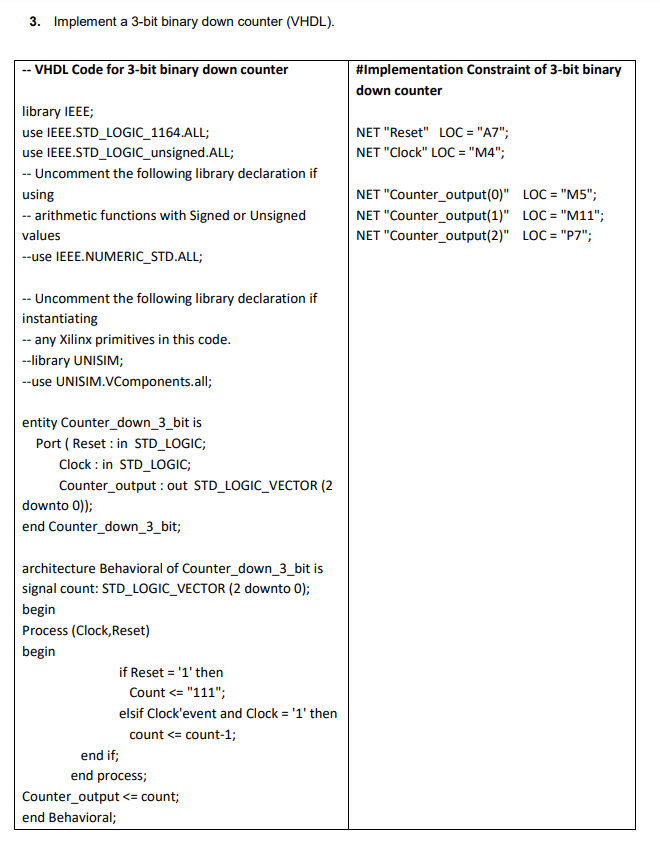

3. Implement a 3-bit binary down counter (VHDL). -- VHDL Code for 3-bit binary down counter #Implementation Constraint of 3-bit binary down counter NET "Reset" LOC = "A7"; NET "Clock" LOC = "M4"; library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_unsigned.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; NET "Counter_output(0)" LOC = "M5"; NET "Counter_output(1)" LOC = "M11"; NET "Counter_output(2)" LOC = "27"; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity Counter_down_3_bit is Port (Reset : in STD_LOGIC; Clock: in STD_LOGIC; Counter_output: out STD_LOGIC_VECTOR (2 downto 0)); end Counter_down_3_bit; architecture Behavioral of Counter_down_3_bit is signal count: STD_LOGIC_VECTOR (2 downto 0); begin Process (Clock, Reset) begin if Reset = '1' then Count

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts