Question: Please help An S-R flip flop is implemented with NOR gates. The flip-flop's transitions are trigger by a clock input signal on the rising edge,

Please help

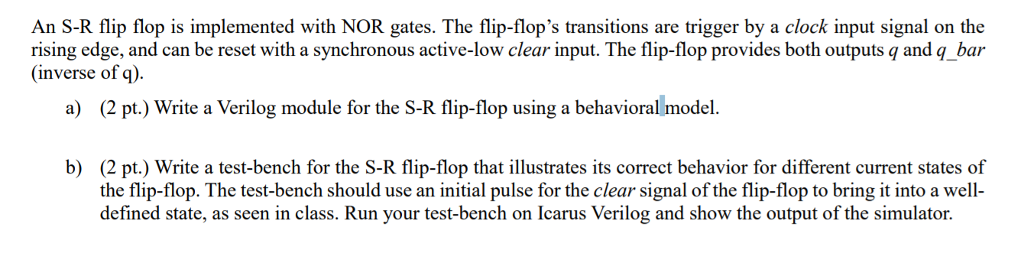

An S-R flip flop is implemented with NOR gates. The flip-flop's transitions are trigger by a clock input signal on the rising edge, and can be reset with a synchronous active-low clear input. The flip-flop provides both outputs q and q bar (inverse of q) a) (2 pt.) Write a Verilog module for the S-R flip-flop using a behavioral model. (2 pt.) Write a test-bench for the S-R flip-flop that illustrates its correct behavior for different current states of the flip-flop. The test-bench should use an initial pulse for the clear signal of the flip-flop to bring it into a well- defined state, as seen in class. Run your test-bench on Icarus Verilog and show the output of the simulator. b) An S-R flip flop is implemented with NOR gates. The flip-flop's transitions are trigger by a clock input signal on the rising edge, and can be reset with a synchronous active-low clear input. The flip-flop provides both outputs q and q bar (inverse of q) a) (2 pt.) Write a Verilog module for the S-R flip-flop using a behavioral model. (2 pt.) Write a test-bench for the S-R flip-flop that illustrates its correct behavior for different current states of the flip-flop. The test-bench should use an initial pulse for the clear signal of the flip-flop to bring it into a well- defined state, as seen in class. Run your test-bench on Icarus Verilog and show the output of the simulator. b)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts