Question: plz solve it urgently Q1. Consider a small computing system with a customized 19 bits ISA CPU for the following MIPS Codes: addi$t1,$t1, 1 begszero,

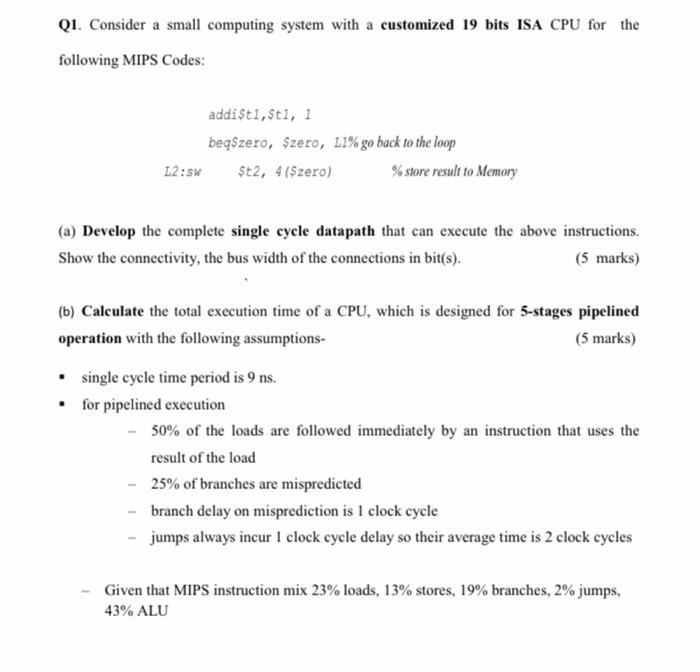

Q1. Consider a small computing system with a customized 19 bits ISA CPU for the following MIPS Codes: addi$t1,$t1, 1 begszero, Szero, L1% go back to the loop L2:SW $t2, 4($zero) % store result to Memory (a) Develop the complete single cycle datapath that can execute the above instructions. Show the connectivity, the bus width of the connections in bit(s). (5 marks) (b) Calculate the total execution time of a CPU, which is designed for 3-stages pipelined operation with the following assumptions- (5 marks) single cycle time period is 9 ns. for pipelined execution 50% of the loads are followed immediately by an instruction that uses the result of the load 25% of branches are mispredicted branch delay on misprediction is 1 clock cycle jumps always incur 1 clock cycle delay so their average time is 2 clock cycles Given that MIPS instruction mix 23% loads, 13% stores, 19% branches, 2% jumps, 43% ALU

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts