Question: Plzzz do fast EQU... . Q3.(12 pts) Memory-Mapped IO. Q3-1. (6pts) Consider two-data transfer cases: 1) by CPU and 2) by DMAC. Case 1) CPU-initiated

Plzzz do fast

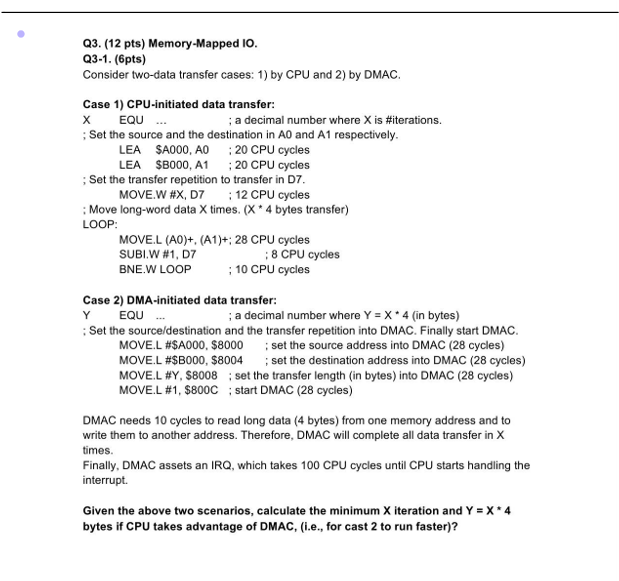

EQU... . Q3.(12 pts) Memory-Mapped IO. Q3-1. (6pts) Consider two-data transfer cases: 1) by CPU and 2) by DMAC. Case 1) CPU-initiated data transfer: x a decimal number where X is #iterations. Set the source and the destination in AO and A1 respectively. LEA SA000, AO 20 CPU cycles LEA $B000, A1 ; 20 CPU cycles ; Set the transfer repetition to transfer in D7. MOVE.W #X, D7 ; 12 CPU cycles : Move long-word data X times. (X* 4 bytes transfer) LOOP: MOVE.L (A0)+. (A1)+: 28 CPU cycles SUBI.W #1, D7 8 CPU cycles BNE.W LOOP ; 10 CPU cycles Case 2) DMA-initiated data transfer: Y EQU a decimal number where Y = X* 4 (in bytes) Set the source/destination and the transfer repetition into DMAC. Finally start DMAC. MOVE.L #$A000, $8000 set the source address into DMAC (28 cycles) MOVE.L #$B000, $8004 ; set the destination address into DMAC (28 cycles) MOVE.L #Y, $8008 set the transfer length (in bytes) into DMAC (28 cycles) MOVE.L #1, $800C ; start DMAC (28 cycles) DMAC needs 10 cycles to read long data (4 bytes) from one memory address and to write them to another address. Therefore, DMAC will complete all data transfer in X times. Finally, DMAC assets an IRQ, which takes 100 CPU cycles until CPU starts handling the interrupt. Given the above two scenarios, calculate the minimum X iteration and Y = X* 4 bytes if CPU takes advantage of DMAC, (i.e., for cast 2 to run faster)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts