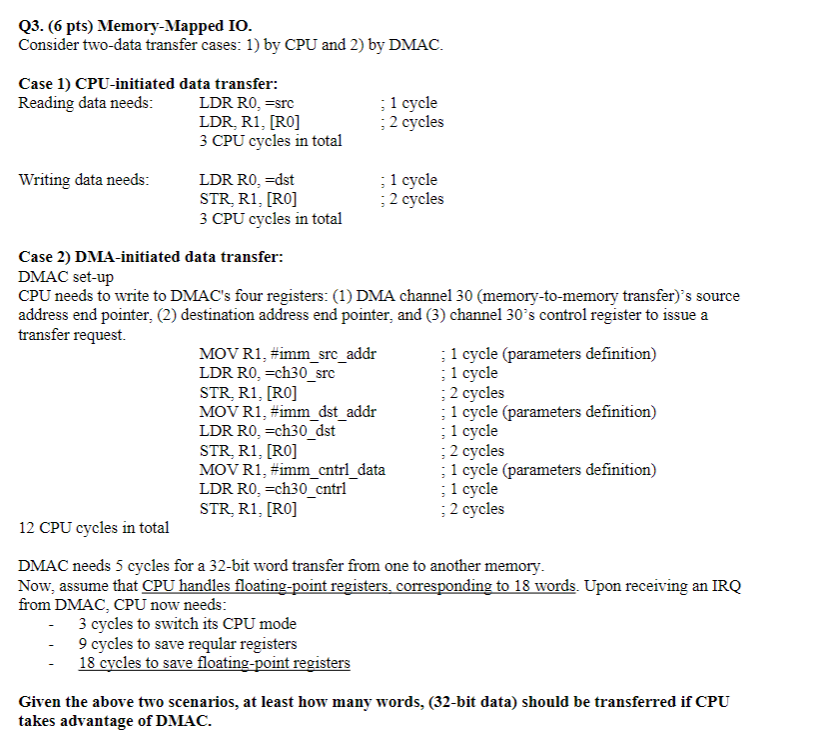

Question: Q 3 . ( 6 pts ) Memory - Mapped IO . Consider two - data transfer cases: 1 ) by CPU and 2 )

Q pts MemoryMapped IO

Consider twodata transfer cases: by CPU and by DMAC.

Case DMAinitiated data transfer:

DMAC setup

CPU needs to write to DMAC's four registers: DMA channel memorytomemory transfers source

address end pointer, destination address end pointer, and channel s control register to issue a

transfer request.

CPU cycles in total

DMAC needs cycles for a bit word transfer from one to another memory.

Now, assume that CPU handles floatingpoint registers, corresponding to words. Upon receiving an IRQ

from DMAC, CPU now needs:

cycles to switch its CPU mode

cycles to save reqular registers

cycles to save floatingpoint registers

Given the above two scenarios, at least how many words, bit data should be transferred if CPU

takes advantage of DMAC.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock