Question: Problem 1: (5 marks) A counter is designed in a way that counts in the following 4-bit sequence: Q=1000, 0111, 0110, 0101, 0100, 0011, 1000,

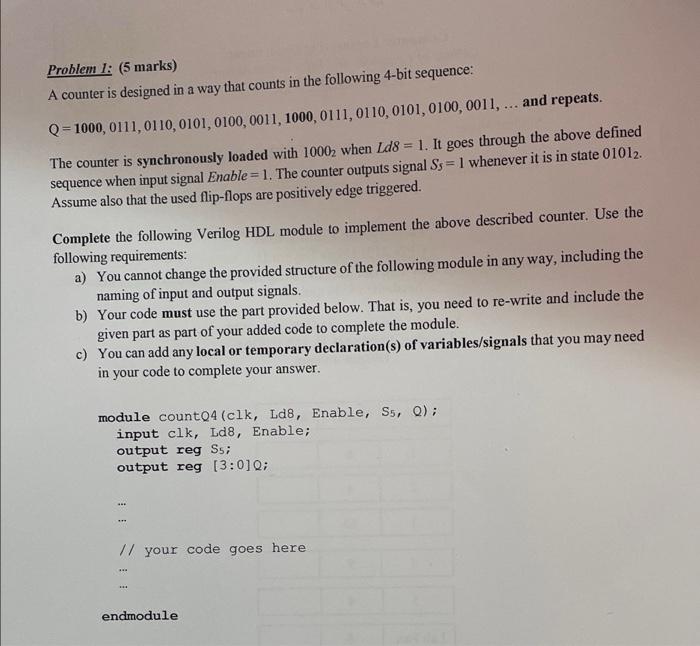

Problem 1: (5 marks) A counter is designed in a way that counts in the following 4-bit sequence: Q=1000, 0111, 0110, 0101, 0100, 0011, 1000, 0111, 0110, 0101, 0100, 0011, ... and repeats. The counter is synchronously loaded with 1000, when Ld8 = 1. It goes through the above defined sequence when input signal Enable = 1. The counter outputs signal Ss=1 whenever it is in state 01012. Assume also that the used flip-flops are positively edge triggered. Complete the following Verilog HDL module to implement the above described counter. Use the following requirements: a) You cannot change the provided structure of the following module in any way, including the naming of input and output signals. b) Your code must use the part provided below. That is, you need to re-write and include the given part as part of your added code to complete the module. c) You can add any local or temporary declaration(s) of variables/signals that you may need in your code to complete your answer. module count04 (clk, Ld8, Enable, S5, 0); input clk, Ld8, Enable; output reg Ss; output reg [3:0]Q; 11 // your code goes here endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts