Question: Problem #1 Consider a multiple-issue design. Suppose you have two execution pipelines, each capable of beginning execution of one instruction per cycle,and enough fetch/decode bandwidth

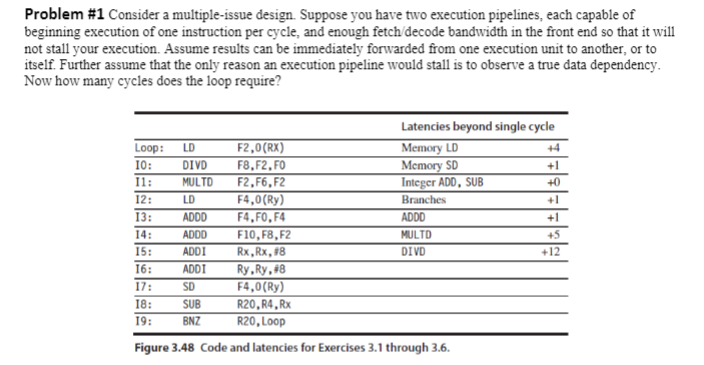

Problem #1 Consider a multiple-issue design. Suppose you have two execution pipelines, each capable of beginning execution of one instruction per cycle,and enough fetch/decode bandwidth in the front end so that it will not stall your execution. Assume results can be immediately forwarded from one execution unit to another, or to itself. Further assume that the only reason an execution pipeline would stall is to observe a true data dependency. Now how many cycles does the loop require?

Problem #1 Consider a multiple-issue design. Suppose you have two execution pipelines, each capable of beginning execution of one instruction per cycle, and enough fetch/decode bandwidth in the front end so that it will not stall your execution. Assume results can be immediately forwarded from one execution unit to another, or to itself. Further assume that the only reason an execution pipeline would stall is to observe a true data dependency. Now how many cycles does the loop require? Latencies beyond single cycle Loop: LD F2,0(RX) Memory LD 10: DIVD F8,F2, F0 Memory SD +1 11: MULTD F2,F6,F2 Integer ADD, SUB +0 12: LD F4,0(Ry) Branches 13: ADDD F4,FO,F4 ADDD +1 ADDD F10, F8, F2 MULTD 15: ADDI Rx, Rx, 18 DIVD +12 16: ADDI Ry, Ry, 8 17: SD F4,0(Ry) 18: SUB R20, R4, RX 19: BNZ R20, Loop Figure 3.48 Code and latencies for Exercises 3.1 through 3.6. 14

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts